日本国特許庁/// PATENT OFFICE /-5.02 JAPANESE GOVERNMENT 別紙添付の書類に記載されている事項は下記の出願書類に記載されて いる事項と同一であることを証明する。 This is to certify that the annexed is a true copy of the following application as filed

3

出 願 年 月 日 Date of Application:

with this Office.

2000年 7月21日

出 願 番 号 Application Number:

特願2000-221207

出 願 人 Applicant (s):

日本電気株式会社

2001年 4月 6日

| 特許願                     |

|-------------------------|

| 71110432                |

| 平成12年 7月21日             |

| 特許庁長官殿                  |

| H03K 5/00               |

| H04L 7/00               |

| G01F 1/10               |

| H03K 19/177             |

|                         |

| 東京都港区芝五丁目7番1号 日本電気株式会社内 |

| 佐伯 貴範                   |

|                         |

| 000004237               |

| 日本電気株式会社                |

|                         |

| 100080816               |

|                         |

| 加藤 朝道                   |

| 045-476-1131            |

|                         |

| 030362                  |

| 21,000円                 |

|                         |

| 明細書 1                   |

|                         |

図面 1

要約書 1

9304371

要

5

4

1

Ļ

【物件名】

【物件名】

【プルーフの要否】

【包括委任状番号】

出証特2001-3028385

特2000-22120

明細書

【発明の名称】 クロック制御方法及び回路

【特許請求の範囲】

【書類名】

【請求項1】

入力クロック又は前記入力クロックから生成されるクロックを基準のクロック として、前記基準のクロックの周期毎に、前記基準のクロックに対して、あらか じめ定められた所定の単位位相差分、加算又は減算してなる位相を有する出力ク ロックを生成出力する手段を備えたことを特徴とするクロック制御回路。

【請求項2】

入力クロック又は前記入力クロックから生成されるクロックを基準のクロック として、前記基準のクロックの周期毎に、前記基準のクロックに対する位相を、 所定の単位位相差分、加算又は減算するための制御信号を出力する制御手段と、

前記入力クロックを入力し、前記制御信号に基づき、前記基準のクロックに対して、あらかじめ定められた所定の単位位相差分、加算又は減算してなる位相を 有する出力クロックを生成出力する位相調整手段と、

を備え、前記基準のクロックの周波数に対して非整数の関係にある周波数の出 カクロックを出力可能とした、ことを特徴とするクロック制御回路。

【請求項3】

入力クロックに対する出力クロックの位相差を、単位位相差毎に、加算又は減 算するための制御信号を生成する制御回路と、

前記入力クロックを入力し、前記制御回路からの前記制御信号に基づき、前記 制御信号で規定される位相差を有する出力クロックを生成出力する位相調整回路 と、

を備えたことを特徴とするクロック制御回路。

【請求項4】

入力クロックを分周してなる分周クロックを出力する分周回路と、

前記分周回路から出力される分周クロックに基づき、前記分周クロックに対す る位相差を、単位位相差毎に、加算又は減算するための制御信号を生成する制御 回路と、

出証特2001-3028385

特2000-22120

前記入力クロックを入力し、前記制御回路からの制御信号で規定される位相の 出力クロックを生成出力する位相調整回路と、

を備えたことを特徴とするクロック制御回路。

【請求項5】

入力クロックから互いに位相が異なる第1乃至第Nのクロック(「多相クロッ ク」という)を生成出力する多相クロック生成回路と、

前記第1乃至第Nのクロックを入力してその一つを選択出力するセレクタと、 前記入力クロックを入力し、前記セレクタにおいて、前記第1乃至第Nのクロ ックを、順次、選択する選択信号を生成して前記セレクタに供給する制御回路と

を備えたことを特徴とするクロック制御回路。

【請求項6】

前記単位位相差が、外部から入力されるモード信号により可変に設定される、 ことを特徴とする請求項1乃至4のいずれか一に記載のクロック制御回路。

【請求項7】

前記セレクタの選択を制御する選択信号の出力が、前記制御回路に入力される モード信号により可変に設定される、ことを特徴とする請求項5に記載のクロッ ク制御回路。

【請求項8】

入力クロックに基づき、該入力クロックを通倍してなる互いに位相の異なる第 1乃至第Nのクロック(「多相逓倍クロック」という)を生成する多相逓倍クロ ック生成回路と、

前記多相逓倍クロック生成回路から出力される前記第1乃至第Nのクロックの うち二つのクロック信号を選択するスイッチと、

前記スイッチから選択出力される二つのクロック信号を入力し、前記二つのク ロック信号のタイミング差を分割した信号を出力する、少なくとも一つのインタ ーポレータと、を備え、前記インターポレータは、そのタイミング差を分割する 内分比が可変に設定可能とされており、

前記スイッチの切り替え信号、及び、前記インターポレータのタイミング差の

出証特2001-3028385

内分比を可変に設定する制御信号を出力する制御回路と、

を備えたことを特徴とするクロック制御回路。

【請求項9】

入力クロックに基づき、該入力クロックを逓倍してなる互いに位相の異なる第 1乃至第Nのクロック(「多相逓倍クロック」という)を生成する多相逓倍クロ ック生成回路と、

前記多相逓倍クロック生成回路から出力される前記第1乃至第Nのクロックの 隣接する二つのクロック信号を、二組選択するスイッチと、

前記スイッチから出力される第1組の二つのクロック信号を入力し、前記二つ のクロック信号のタイミング差を分割した信号を出力する第1のインターポレー タと、

前記スイッチから出力される第2組の二つのクロック信号を入力し、前記二つ のクロック信号のタイミング差を分割した信号を出力する第2のインターポレー タと、

前記第1、及び第2のインターポレータの出力を入力し、前記二つの出力のタ イミング差を分割した信号を出力する第3のインターポレータと、を備え、

前記第1乃至第3のインターポレータの少なくとも一つは、前記インターポレ ータのタイミング差を分割する内分比が可変に設定可能とされており、

前記スイッチの切り替え信号、及び、前記インターポレータのタイミング差の の内分比を可変に設定する制御信号を出力する制御回路と、

を備えたことを特徴とするクロック制御回路。

【請求項10】

入力クロックを入力し、前記入力クロックを分周した互いに位相の異なる二組 のクロックを生成する分周回路と、

前記分周回路から出力される第1組の二つのクロック信号を入力し、前記二つ のクロック信号のタイミング差を分割した信号を出力する第1のインターポレー タと、

前記分周回路から出力される第2組の二つのクロック信号を入力し、前記二つ のクロック信号のタイミング差を分割した信号を出力する第2のインターポレー

出証特2001-3028385

特2000-22120

タと、

前記第1、及び第2のインターポレータの出力を入力し、前記二つの出力のタ イミング差を分割した信号を出力する第3のインターポレータと、を備え、

前記第1乃至第3のインターポレータの少なくとも一つは、前記インターポレ ータのタイミング差を分割する内分比が可変に設定可能とされており、

前記スイッチの切り替え信号、及び、前記インターポレータのタイミング差の 内分比を可変に設定する制御信号を出力する制御回路と、

を備えたことを特徴とするクロック制御回路。

【請求項11】

入力クロックに基づき、該入力クロックを逓倍してなる互いに位相の異なる複 数のクロック(「多相逓倍クロック」という)を生成する多相逓倍クロック生成 回路と、

前記多相逓倍クロック生成回路から出力される前記複数のクロックのうち、互 いに隣接する位相の二つのクロックを入力し、該二つのクロックのタイミング差 を、それぞれ互いに異なる所定の内分比で分割した信号をそれぞれ出力する複数 インターポレータと、

複数の前記インターポレータの出力を入力しこれらを多重化して一つの出力信 号として出力する合成器と、

を備えたことを特徴とするクロック制御回路。

【請求項12】

前記多相逓倍クロック生成回路がN相(ただし、Nは所定の正整数)のクロッ クを生成し、前記インターポレータをM個(ただし、Mは、M≦Nなる正整数) 備え、i番目の前記インターポレータには、i番目とi+1番目のクロック(た だし、iは1~Mの整数、なお、n+1番目のクロックは1番目のクロックとな る)が入力され、

前記各インターポレータにおける二つの入力信号のタイミング差を分割する内 分比は、 i 番目の前記インターポレータよりも i + 1 番目の前記インターポレー タの方が、所定単位ステップ分、大又は小の値に設定されており、

M個の前記インターポレータからM相のクロックが出力され、

出証特2001-3028385

前記合成器から、M逓倍のクロックが出力される、構成としてなる、ことを特 徴とする請求項11記載のクロック制御回路。

【請求項13】

前記多相クロック生成回路が、前記入力クロックを分周して多相クロックを生 成し該多相クロックを逓倍した信号を生成する前記多相逓倍クロック生成回路よ りなる、ことを特徴とする請求項5記載のクロック制御回路。

【請求項14】

前記多相逓倍クロック生成回路が、入力クロックを分周して互いに位相の異な る複数のクロック(「多相クロック」という)を生成出力する分周回路と、

前記入力クロックの周期を検知する周期検知回路と、

前記分周回路から出力される多相クロックを入力とし、前記クロックを逓倍し た多相クロックを生成する多相クロック逓倍回路と、を備え、

前記多相クロック逓倍回路が、二つの入力のタイミング差を分割した信号を出 力する複数のタイミング差分割回路と、二つの前記タイミング差分割回路の出力 をそれぞれ多重化して出力する複数の多重化回路とを備え、

前記複数のタイミング差分割回路は、同一位相のクロックを入力とするタイミング差分割回路と、相隣る位相の二つのクロックを入力とするタイミング差分割 回路を備えている、ことを特徴とする請求項8、9、13のいずれかーに記載の クロック制御回路。

【請求項15】

前記多相クロック逓倍回路が、 n 相のクロック(第1乃至第 n クロック)を入 力し、

二つの入力のタイミング差を分割した信号を出力する2n個のタイミング差分 割回路を備え、

2 I-1番目(ただし、1≤I≤n)のタイミング差分割回路は、前記二つの 入力としてI番目の同一クロックを入力とし、

2 I番目(ただし、1≤I≤n)のタイミング差分割回路は、I番目のクロックと、(I+1 mod n)番目(ただし、modは剰余演算を表し、I+1 mod nは、I+1をmで割った余り)のクロックを入力とし、

出証特2001-3028385

J番目(ただし、 $1 \leq J \leq 2 n$ )のタイミング差分割回路の出力と(J+2 mod n)番目(ただし、J+2 mod nは、J+2をnで割った余り) のタイミング差分割回路の出力とを入力とする2n個のパルス幅補正回路と、

K番目(ただし、1≦K≦n)のパルス幅補正回路の出力と(K+n)番目の パルス幅補正回路の出力とを入力とするn個の多重化回路と、

を備えた、ことを特徴とする請求項14記載のクロック制御回路。

【請求項16】

前記タイミング差分割回路が、第1、第2の入力信号を入力とする否定論理和 回路と、

前記否定論理和回路の出力である内部ノードの電位を入力とするインバータと 、を備え、

前記内部ノードと接地間に、直列接続されたスイッチ素子と容量とが、複数本 互いに並列接続されており、

前記スイッチの制御端子に接続する周期制御信号にて前記内部ノードに付加す る容量を決められる構成とされている、ことを特徴とする請求項14又は15に 記載のクロック制御回路。

【請求項17】

前記タイミング差分割回路が、第1、第2の入力信号を入力とし前記第1及び 第2の入力信号の所定の論理演算結果を出力する論理回路と、

第1の電源と内部ノード間に接続され、前記論理回路の出力信号を制御端子に 入力とする第1のスイッチ素子と、

前記内部ノードに入力端が接続され、前記内部ノード電位としきい値との大小 関係が反転した場合に出力論理値を変化させるバッファ回路と、

前記内部ノードと第2の電源との間に直列に接続される、第1の定電流源、及び、前記第1の入力信号によりオン・オフ制御される第2のスイッチ素子と、

前記内部ノードと前記第2の電源との間に直列に接続される、第2の定電流源 、及び、前記第2の入力信号によりオン・オフ制御される第3のスイッチ素子と

## を備え、

出証特2001-3028385

特2000-22120

さらに前記内部ノードと前記第2の電源間には、直列接続された第4のスイッ チ素子と容量とが、複数本互いに並列接続され、前記第4のスイッチ素子の制御 端子に供給される周期制御信号にて前記内部ノードに付加する容量が決められる 、ことを特徴とする請求項14又は15に記載のクロック制御回路。

【請求項18】

前記第1のスイッチ素子が、第1導電型のMOSトランジスタよりなり、 前記第2乃至第4のスイッチ素子が、第2導電型のMOSトランジスタよりな る、ことを特徴とする請求項17に記載のクロック制御回路。

【請求項19】

クロック信号を分周回路で分周した信号と、該分周信号を所定クロック周期分 送られた信号と、を入力し、前記二つの入力信号のタイミング差を所定の内分比 で分割した信号を出力するインターポレータを備え、

前記インターポレータはタイミング差の内分比が可変に設定可能とされており

前記クロック信号に基づき、前記インターポレータにおけるタイミング差の内 分比を可変させる制御回路を備えたことを特徴とするクロック制御回路。

【請求項20】

二つの入力信号のタイミング差をそれぞれ互いに異なる値の所定の内分比で分割した信号を出力するインターポレータを複数(N個)備え、

互いに相の異なる第1乃至第Nのクロックについて、I番目とI+1番目(但 し、Iは1からNの整数であり、N+1番目は1番目となる)の二つのクロック がそれぞれI番目の前記インターポレータに入力される、ことを特徴とするクロ ック制御回路。

【請求項21】

前記インターポレータが、第1、及び第2の入力信号を入力とし前記第1及び 第2の入力信号の所定の論理演算結果を出力する論理回路と、

第1の電源と内部ノードとの間に接続され、前記論理回路の出力信号を制御端 子に入力とし、前記第1、及び第2の入力信号がともに第1の値のとき、オン状 態とされる第1のスイッチ素子と、

出証特2001-3028385

前記内部ノードが入力端に接続され、前記内部ノードの容量の端子電圧としき い値との大小関係が反転した場合に出力論理値を変化させるバッファ回路と、

を備え、

前記内部ノードと第2の電源との間には、前記第1の入力信号が第2の値のと きオン状態とされる第2のスイッチ素子と、前記制御回路からの制御信号に基づ きそれぞれオン・オフ制御される前記第3のスイッチ素子と、第1の定電流源よ りなる直列回路を、複数個並列に備え、

前記内部ノードと前記第2の電源との間には、さらに、前記第2の入力信号が 第2の値のとき共通にオン状態とされる第4のスイッチ素子と、前記制御回路か らの制御信号に基づきそれぞれオン・オフ制御される前記第5のスイッチ素子と 、定電流源よりなる直列回路を、複数個並列に備えている、ことを特徴とする請 求項8、9、10、11、12、19、20のいずれか一に記載のクロック制御 回路。

【請求項22】

前記インターポレータが、第1、及び第2の入力信号を入力とし前記第1及び 第2の入力信号の所定の論理演算結果を出力する論理回路と、

第1の電源と内部ノードとの間に接続され、前記論理回路の出力信号を制御端 子に入力とし、前記第1、及び第2の入力信号がともに第1の値のとき、オン状 態とされる第1のスイッチ素子と、

前記内部ノードが入力端に接続され、前記内部ノードの容量の端子電圧としき い値との大小関係が反転した場合に出力論理値を変化させるバッファ回路と、

を備え、

前記内部ノードと第2の電源との間には、前記第1の入力信号が第2の値のと きオン状態とされる第2のスイッチ素子と、前記制御回路からの制御信号に基づ きそれぞれオン・オフ制御される前記第3のスイッチ素子と、第1の定電流源よ りなる直列回路を、複数個並列に備え、

前記内部ノードと前記第2の電源との間には、前記第2の入力信号が第2の値 のとき共通にオン状態とされる第4のスイッチ素子と、前記制御回路からの制御 信号に基づきそれぞれオン・オフ制御される前記第5のスイッチ素子と、定電流

出証特2001-3028385

特2000-22120

源よりなる直列回路を、複数個並列に備え、

前記内部ノードと前記第2の電源間には、さらに、直列接続された第6のスイ ッチ素子と容量とが、複数本互いに並列接続され、前記第6のスイッチ素子の制 御端子に供給される周期制御信号にて前記内部ノードに付加する前記容量の値が 選択的に決められる、ことを特徴とする請求項8、9、10、11、12、19

、20のいずれかーに記載のクロック制御回路。

【請求項23】

前記第2のスイッチ素子、前記第3のスイッチ素子、前記第4のスイッチ素子、 、及び、前記第5のスイッチ素子がいずれも少なくとも所定個数(N個)よりな り、

前記第3のスイッチ素子群に供給する制御信号により、K個(但しKは0~N))の前記第3のスイッチ素子をオンとし、

前記第5のスイッチ素子群に供給する制御信号により、N-K個の前記第5の スイッチ素子をオンとし、

前記第1の入力信号と前記第2の入力信号のタイミング差を、前記タイミング 差のN分の1を単位として前記Kに基づく内分したタイミングに対応する信号を 出力し、前記Kの値を可変することで、前記タイミング差の内分比が可変される 、ことを特徴とする請求項21又は22に記載のクロック制御回路。

【請求項24】

前記第3のスイッチ素子の制御端子に、前記制御回路から供給される制御信号 を、インバータで反転した信号が、前記第3のスイッチ素子に対応する前記第5 のスイッチ素子の制御端子に制御信号として供給される、ことを特徴とする請求 項23に記載のクロック制御回路。

【請求項25】

前記第1のスイッチ素子が、第1導電型のMOSトランジスタよりなり、

前記第2乃至第5のスイッチ素子が、第2導電型のMOSトランジスタよりなる、ことを特徴とする請求項21に記載のクロック制御回路。

【請求項26】

前記第1のスイッチ素子が、第1導電型のMOSトランジスタよりなり、

前記第2乃至第6のスイッチ素子が、第2導電型のMOSトランジスタよりなる、ことを特徴とする請求項22に記載のクロック制御回路。

【請求項27】

前記周期制御信号が、請求項14の前記周期検知回路から供給される、ことを 特徴とする請求項22に記載のクロック制御回路。

【請求項28】

入力クロック又は前記入力クロックから生成されるクロックを基準のクロック として、前記基準のクロックの周期毎に、前記基準のクロックに対して、あらか じめ所定の単位位相差分、加算又は減算してなる位相の出力クロックを出力する 、ことを特徴とするクロック制御方法。

【請求項29】

前記基準のクロックの周波数に対して非整数の関係にある周波数の出力クロックを出力可能とした、ことを特徴とする請求項28記載のクロック制御方法。

【請求項30】

入力クロックを分周回路で分周し、前記分周されたクロックに基づき、前記分 周クロックに対する位相差を、単位位相差ごとに加算又は減算するための制御信 号を生成し、前記分周クロックに対して、前記制御信号で設定される位相差の信 出力クロックを生成する、ことを特徴とするクロック制御方法。

【請求項31】

前記単位位相差が、制御信号により可変に設定される、ことを特徴とする請求 項28乃至30のいずれか一に記載のクロック制御方法。

【請求項32】

入力クロックから互いに位相が異なる第1乃至第Nのクロック(「多相クロッ ク」という)を生成してセレクタに入力し、セレクタにおいて、前記第1乃至第 Nのクロックを、順次、選択出力する、ことを特徴とするクロック制御方法。

【請求項33】

二つのクロック信号のタイミング差を分割した信号を出力するインターポレー タで、前記出力クロックの位相を調整し、前記インターポレータのタイミング差 を分割する内分比を可変させることで、クロックの周波数に対して非整数の関係

出証特2001-3028385

にある周波数の出力クロックを出力可能とした、ことを特徴とする請求項28乃 至30のいずれかーに記載のクロック制御方法。

【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、クロック制御回路及び方法に関する。

[0002]

【従来の技術】

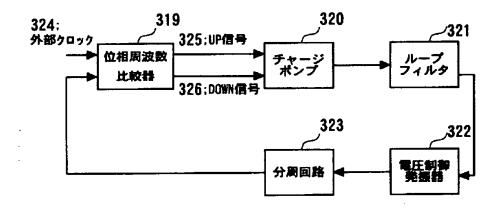

クロック周期を調整する回路は、PLL (Phase Locked Loop;位相同期ル ープ)回路を備えて構成とされている。図27は、従来のPLL回路の構成を示 す図である。図27を参照すると、外部クロック324と、電圧制御発振器32 2の出力を分周回路323で分周した信号が位相周波数検出回路 (Phase Frequ ency Detector; PFD) 319に入力され、位相差に応じた電圧をチャージポ ンプ320が出力し、ループフィルタ321で平滑化された電圧が電圧制御発振 器 (Voltage Controlled Oscillator; VCO) 322に制御電圧として供給 され、該制御電圧に応じた周波数の出力クロックが電圧制御発振器322から分 周回路323に供給される。

[0003]

例えば特開平11-284497号公報には、遅延時間を決定するためのラン プ波電圧、及び閾値電圧を同一構成の回路で発生させることができ、またランプ 波電圧と閾値電圧をそれぞれ独立に設定できるので、分子分母の両者が設定可能 な分数の遅延時間を発生させることができるプログラマブル遅延発生器、該プロ グラマブル遅延発生器を使用してアキュムレータの出力パルスの位相補間を行う ことにより、無調整で、低スプリアスな出力信号を発生できる周波数シンセサイ ザ、該プログラマブル遅延発生器を用いた逓倍回路、該プログラマブル遅延発生 器を、出力パルス幅を決定する遅延発生器に用いたデューティ比変換回路、該プ ログラマブル遅延発生器を分周器と位相比較器の間に挿入したPLL周波数シン セサイザ等が提案されている。

[0004]

特2000-22120

【発明が解決しようとする課題】

しかしながら、図27に示した従来の回路は、PLL回路を備え、帰還系回路 を用いているため、位相調整に時間を要するほか、帰還系特有のジッタがある、 という問題点を有している。

[0005]

また、上記した従来のプログラマブル遅延発生器には、閾値電圧発生回路等の 電源電圧発生回路が必要とされている。このため、回路規模が増大するという問 題点を有している。

[0006]

したがって、本発明は、上記問題点に鑑みてなされたものであって、その目的 は、簡易な構成により、高精度に、非整数の周波数変換を行うことができるクロ ック制御回路及び方法を提供することにある。

[0007]

【課題を解決するための手段】

前記目的を達成する本発明は、クロックを入力し、一定周期毎に、前記クロックに対する位相差をあらかじめ定められた所定の単位位相差加算又は減算してなる位相差を有する出力クロックを出力するものである。

[0008]

本発明は、入力クロック又は前記入力クロックから生成されるクロックを基準 のクロックとして、前記基準のクロックの周期毎に、前記基準のクロックに対す る位相を、所定の単位位相差分加算又は減算するための制御信号を出力する制御 手段と、前記入力クロックを入力し、前記制御信号に基づき、前記基準のクロッ クに対して、あらかじめ定められた所定の単位位相差分、加算又は減算してなる 位相を有する出力クロックを生成出力する位相調整手段と、を備え、前記基準の クロックの周波数に対して非整数の関係にある周波数の出力クロックを出力可能 としている。

[0009]

本発明においては、入力クロックを分周してなる分周クロックを出力する分周 回路と、前記分周回路から出力される分周クロックに基づき、前記分周クロック

特2000-22120♥

に対する位相差を、単位位相差毎に、加算又は減算するための制御信号を生成す る制御回路と、前記入力クロックを入力し、前記制御回路からの制御信号で設定 される位相の信号を生成出力する位相調整回路と、を備えた構成としてもよい。

[0010]

本発明においては、入力クロックから互いに位相が異なる第1乃至第Nのクロ ック(「多相クロック」という)を生成出力する多相クロック生成回路と、前記 第1乃至第Nのクロックを入力してその一つを選択出力するセレクタと、前記入 カクロックを入力し、前記セレクタにおいて、前記第1乃至第Nのクロックを、 順次、選択する選択信号を生成して前記セレクタに供給する制御回路と、を備え た構成としてもよい。上記目的は、特許請求の範囲の各請求項の発明によって同 様に達成されることは、以下の実施の形態及び実施例等の説明から、当業者には 直ちに明らかとされるであろう。

[0011]

【発明の実施の形態】

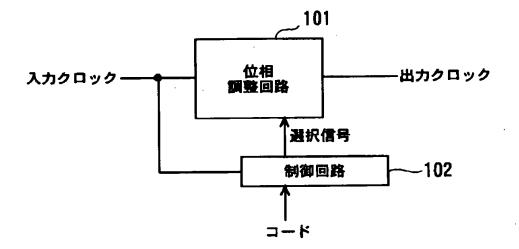

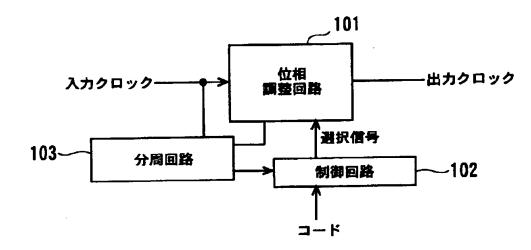

本発明の実施の形態について以下に説明する。本発明の一実施の形態は、入力 クロック又は前記入力クロックから生成されるクロックを基準のクロックとして 、前記基準のクロックのクロック周期毎に、前記基準のクロックに対する位相を あらかじめ所定の単位位相差分加算又は減算するための選択信号を出力する制御 回路(図1の102)と、前記入力クロックを入力し、前記選択信号に基づき、 前記基準のクロックに対して前記加算されてなる位相を有するクロックを出力す る位相調整回路(図1の101)と、を備える。

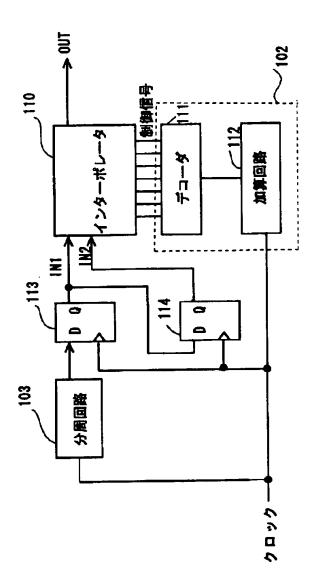

[0012]

本発明は、別の実施の形態において、入力クロックを分周する分周回路(図3 の103)と、前記分周回路で分周されたクロックに基づき、前記分周クロック に対する位相差を、単位位相差ごとに加算又は減算するための制御信号を生成す る制御回路(図3の102)と、入力クロックを入力し、前記入力クロック信号 に対して、前記制御回路からの制御信号で設定される位相の信号を生成する位相 調整回路(図3の101)と、を備える。

[0013]

特2000-22120♥

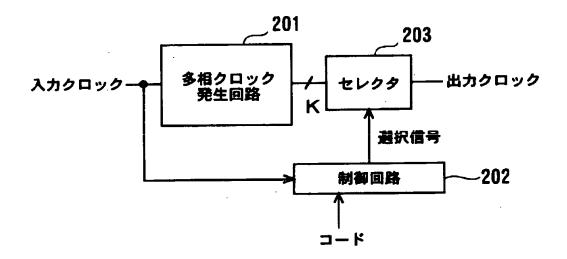

本発明は、別の実施の形態において、入力クロックから互いに位相が異なる第 1乃至第Nのクロック(「多相クロック」という)を生成する多相クロック生成 回路(図4の201)と、前記第1乃至第Nのクロックを入力してその一つを選 択出力するセレクタ(図4の203)と、前記入力クロックを入力し、前記セレ クタにおいて、前記第1乃至第Nのクロックを、順次、選択する選択信号を供給 する制御回路(図4の202)と、を備える。

[0014]

本発明においては、位相調整回路を、入力される二つの信号のタイミング差を 分割し信号を出力するインターポレータで構成し、クロック信号を分周回路で分 周した信号と該分周信号を所定クロック周期分送られた信号とをインターポレー タに入し、前記クロック信号に基づき、前記インターポレータにおけるタイミン グ差の分割値を可変させる制御回路を備える。

[0015]

二つの入力信号のタイミング差を分割した信号を出力するインターポレータを 複数備え、前記複数のインターポレータにおけるタイミング差の分割値は互いに 異なる値に設定され、互いに相の異なる複数(N個)のクロックについて、複数 組の二つのクロックがそれぞれ前記複数のインターポレータに入力され、一のイ ンターポレータにおいて、両端の第1と第Nのクロックを入力とする構成として もよい。

[0016]

本発明は、別の実施の形態において、入力クロックに基づき前記入力クロック の周波数を逓倍した互いに位相の異なる第1乃至第Nのクロック(「多相逓倍ク ロック」という)を生成する多相逓倍クロック生成回路(図20の10)と、前 記第1乃至第Nのクロックのうち二つのクロック信号を選択するスイッチ(図2 0の20)と、前記スイッチから選択出力される二つクロック信号を入力し、前 記二つのクロック信号のタイミング差を分割した信号を出力するインターポレー タ(図20の30)と、前記スイッチの切り替え及びインターポレータのタイミ ング分割値を設定する制御信号を出力する制御回路(図20の40)とを備える

出証特2001-3028385

特2000-22120

## [0017]

本発明は、さらに別の実施の形態において、入力クロックに基づき前記入力ク ロックを一旦分周して多相クロックを生成し、該多相クロックの周波数を逓倍し た互いに位相の異なる第1乃至第Nのクロック(「多相逓倍クロック」という) を生成する多相逓倍クロック生成回路(図22の10)と、前記第1乃至第Nの クロックの隣接する二つのクロック信号を、二組選択するスイッチ(図22の2 0)と、前記スイッチから出力される第1組の二つのクロック信号を入力し、前 記二つのクロック信号のタイミング差を分割した信号を出力する第1のインター ポレータ(図22の30<sub>1</sub>)と、前記スイッチから出力される第2組の二つのク ロック信号を入力し、前記二つのクロック信号のタイミング差を分割した信号を 出力する第2のインターポレータ(図22の30<sub>2</sub>)と、前記第1、第2のイン ターポレータの出力を入力し、前記二つの出力のタイミング差を分割した信号を 出力する第3のインターポレータ(図22の30<sub>2</sub>)と、前記スイッチの切り替 え及び前記インターポレータのタイミング差分割値を設定する制御信号を出力す る制御回路(図22の40)と、を備える。

[0018]

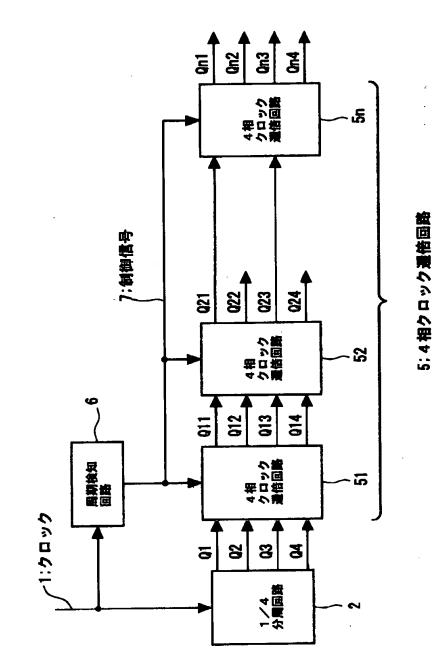

多相逓倍クロック生成回路は、入力クロックを分周して互いに位相の異なる複 数のクロック(「多相クロック」という)を生成出力する分周回路(図5の2) と、入力クロックの周期を検知する周期検知回路(図5の6)と、前記分周回路 から出力される多相クロックを入力とし、前記クロックを逓倍した多相クロック を生成する多相クロック逓倍回路(図5の5)と、を備え、前記多相クロック 値回路(5)は、二つの入力のタイミング差を分割した信号を出力する複数のタ イミング差分割回路(図6の4 a 1~4 a 8)と、二つの前記タイミング差分割 回路の出力をそれぞれ多重化して出力する複数の多重化回路(図6の4 b 1~4 b 4)とを備え、前記複数のタイミング差分割回路は、同一位相のクロックを入 力とするタイミング差分割回路(図6の4 a 1、4 a 3、4 a 5、4 a 7)と、 相隣る位相の二つのクロックを入力とするタイミング差分割回路(図6の4 a 2 、4 a 4、4 a 6、4 a 8)を備えている。

[0019]

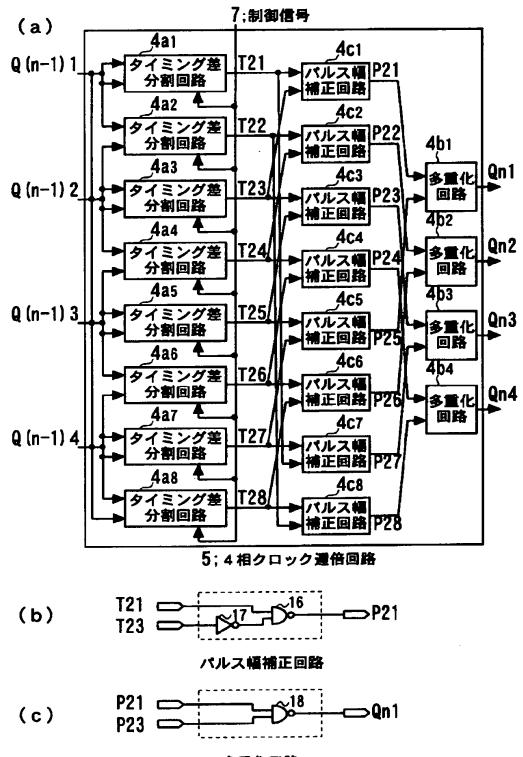

多相クロック逓倍回路(5)は、n相のクロック(第1乃至第nクロック)を 入力し、二つの入力のタイミング差を分割した信号を出力する2n個のタイミン グ差分割回路(図6の4a1~4a8)を備え、2I-1番目(ただし、1≦I ≦n)のタイミング差分割回路(図6の4a1、4a3、4a5、4a7)は、 前記二つの入力としてI番目の同一クロックを入力とし、2I番目(ただし、1 ≦I≦n)のタイミング差分割回路(図6の4a2、4a4、4a6、4a8) は、I番目のクロックと、(I+1 mod n)番目(ただし、modは剰余 演算を表し、I+1 mod nは、I+1をmで割った余り)のクロックを入 力とし、J番目(ただし、1≦J≦2n)のタイミング差分割回路の出力と(J +2 mod n)番目(ただし、J+2 mod nは、J+2をnで割った 余り)のタイミング差分割回路の出力とを入力とする2n個のパルス幅補正回路 (図6の4c1~4c8)と、K番目(ただし、1≦K≦n)のパルス幅補正回路 の出力と(K+n)番目のパルス幅補正回路の出力とを入力とするn個の多重 化回路(図6の4b1~4b4)と、を備えている。

[0020]

本発明は、さらに別の実施の形態において、入力クロックを入力し、前記入力 クロックの分周した互いに位相の異なるクロックを生成する分周回路(図23の 60)と、前記分周回路から出力される第1組の二つのクロック信号を入力し、 前記二つのクロック信号のタイミング差を分割した信号を出力する第1のインタ ーポレータ(図23の30<sub>1</sub>)と、前記スイッチから出力される第2組の二つの クロック信号を入力し、前記二つのクロック信号のタイミング差を分割した信号 を出力する第2のインターポレータ(図23の30<sub>2</sub>)と、前記第1、第2のイ ンターポレータの出力を入力し、前記二つの出力のタイミング差を分割した信号 を出力する第3のインターポレータ(図23の30<sub>3</sub>)と、前記スイッチの切り 替え及び前記インターポレータのタイミング分割値を設定する制御信号を出力す る制御回路(図23の40)と、を備える。

[0021]

本発明は、さらに別の実施の形態において、入力クロックに基づき、該入力ク ロックを逓倍してなる互いに位相の異なる複数のクロックを生成する多相逓倍ク

出証特2001-3028385

ロック生成回路(図24の10)と、多相逓倍クロック生成回路から出力される 複数のクロックのうち、互いに隣接する位相の二つのクロックを入力し、該二つ のクロックのタイミング差をそれぞれ互いに異なる所定の内分比で分割した信号 をそれぞれ出力する複数インターポレータ(図24の30<sub>1</sub>~30<sub>n</sub>)と、複数の インターポレータの出力を入力しこれらを多重化して一つの出力信号として出力 する合成器(図24の50)と、を備えて構成される。

[0022]

この実施の形態において、多相逓倍クロック生成回路がN相(ただし、Nは所 定の正整数)のクロックを生成し、インターポレータ30をM個(ただし、Mは 、M≦Nなる正整数)備え、i番目の前記インターポレータには、i番目とi+ 1番目のクロック(ただし、iは1~Mの整数、なお、n+1番目のクロックは 1番目のクロックとなる)が入力され、各インターポレータにおける二つの入力 信号のタイミング差を分割する内分比は、i番目(ただし、iは1~Mの整数) のインターポレータよりもi+1番目のインターポレータの方が、所定単位ステ ップ分、大又は小の値に設定されており、M個のインターポレータからM相のク ロックが出力され、前記合成器から、M逓倍のクロックが出力される構成として もよい。この場合、各インターポレータにおける二つの入力信号のタイミング差 を分割する内分比は固定値とされる。

[0023]

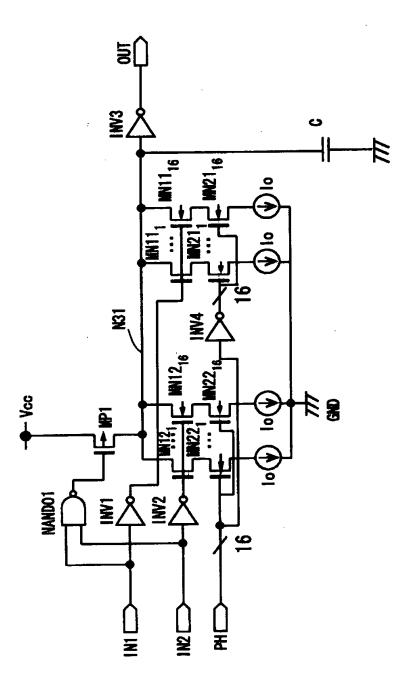

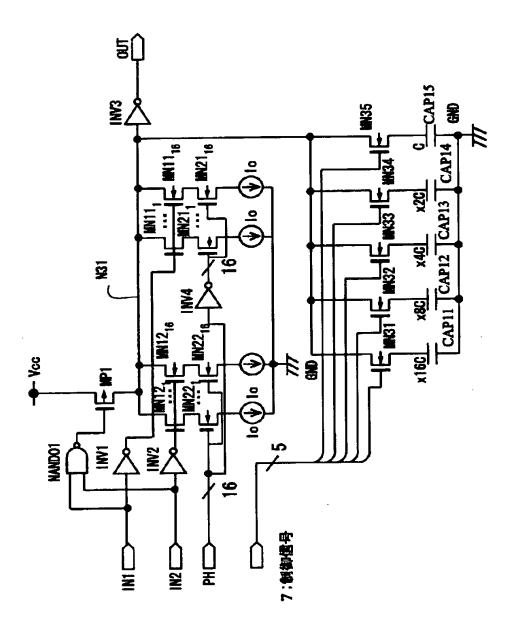

上記した本発明の実施の形態において、インターポレータは、例えば図12乃 至図15を参照すると、第1、及び第2の入力信号を入力とし前記第1及び第2 の入力信号の所定の論理演算結果を出力する論理回路(NANDO1)と、第1の電源 と内部ノード(N31)間に接続され、前記論理回路の出力信号を制御端子に入 力とし、前記第1、及び第2の入力信号が第1の値のとき、オン状態とされる第 1のスイッチ素子(MP1)と、前記内部ノードが入力端に接続され、前記内部ノ ードの容量の端子電圧としきい値との大小関係が反転した場合に出力論理値を変 化させるバッファ回路(INV3)と、前記内部ノードと第2の電源間に直列に 接続され、前記第1の入力信号(IN1)が第2の値のとき共通にオン状態とさ れる第2のスイッチ素子(MN11)と、制御回路(図20の40等)からの制御

出証特2001-3028385

信号(PH)に基づきそれぞれオン・オフ制御される第3のスイッチ素子(MN 21)と、定電流源(I<sub>0</sub>)よりなる直列回路を、複数個並列に備え、前記内部ノ ードと第2の電源間に直列に接続され、前記第2の入力信号が第2の値のとき共 通にオン状態とされる第4のスイッチ素子(MN12)と、前記制御回路からの制 御信号に基づきそれぞれオン・オフ制御される前記第5のスイッチ素子(MN2 2)と、定電流源(I<sub>0</sub>)よりなる直列回路を、複数個並列に備えている。なお、 第3のスイッチ素子(MN21)を内部ノード(N31)側に接続し、第2のスイ ッチ素子(MN11)を定電流源(I<sub>0</sub>)側に接続するように、その配置を入れ替 えてもよいことは勿論であり、第4のスイッチ素子(MN12)と、第5のスイッ チ素子(MN22)の配置を入れ替えてもよいことは勿論である。

【0024】

内部ノード(N31)と前記第2の電源間には、直列接続された第6のスイッ チ素子と容量とが、複数本互いに並列接続され(MN31~MN34、CAP1 1~CAP14)、前記第6のスイッチ素子群(MN31~MN34)の制御端 子に供給される周期制御信号(7)にて、前記内部ノードに付加する前記容量の 値が選択的に決められる。

[0025]

【実施例】

上記した本発明の実施の形態についてさらに詳細に説明すべく、本発明の実施 例について図面を参照して以下に説明する。

[0026]

図1は、本発明の第1の実施例の構成を示す図である。図1を参照すると、本 発明の第1の実施例は、入力クロックを入力し、該入力クロック又は該入力クロ ックから生成される信号を基準のクロックとして、該基準クロックに対して、位 相を調整して、出力クロックを出力する位相調整回路101と、入力クロックと コード情報を入力し、選択信号を、位相調整回路101に出力する加算回路10 2と、を備えている。この位相調整回路101は、後に説明されるように、好ま しくは、タイミング差を分割する内分比が可変に設定されるインターポレータよ り構成される。

`特2000−2212

[0027]

制御回路102は、例えば初期値0から、所定の単位m(m=1、2、3、…)を、入力クロックを入力するたびにインクリメント(0、m、2m、3m、…)する加算回路と、加算結果をデコードし、該加算結果に対応する選択信号(制御信号)を位相調整回路101に出力する。所定の単位mの値は、外部から制御回路102に入力されるコード信号により設定される。

[0028]

なお、制御回路102は、初期値Nから、所定の単位m(m=1、2、3、… )を、入力クロックを入力するたびにデクリメント(N、N-m、N-2m、N -3m、…)する減算回路と、減算回路の減算結果をデコードし、該減算結果に 対応する選択信号(制御信号)を位相調整回路101に出力する構成としてもよ い。

[0029]

位相調整回路101は、制御回路102からの選択信号に基づき、クロック周 期tCKの入力クロックのエッジ(例えば立ち上がりエッジ)に対して、制御回 路102からの選択信号で決定される単位位相差をΔΦとしたとき、該エッジに 対して、0、ΔΦ、2ΔΦ、3ΔΦ、…、(n-1)ΔΦ、nΔΦ、…の位相差 の信号を出力する。ただし、nΔΦは位相差0と等価である。

[0030]

制御回路102からの選択信号mが「1」であるときの単位位相差を $\Delta \Phi$ とした場合、選択信号が「m」のときには、位相調整回路101における単位位相差 はm $\Delta \Phi$ となり、クロック周期tCKの入力クロックのエッジに対して、入力ク ロック毎に、0、m $\Delta \Phi$ 、2m $\Delta \Phi$ 、3m $\Delta \Phi$ 、…、(n-1)m $\Delta \Phi$ 、nm $\Delta$  $\Phi$ 、…の位相の信号を出力する。ただし、単位位相差 $\Delta \Phi$ がtCK/nのとき、 nm $\Delta \Phi$ は、位相差0と等価である。

[0031]

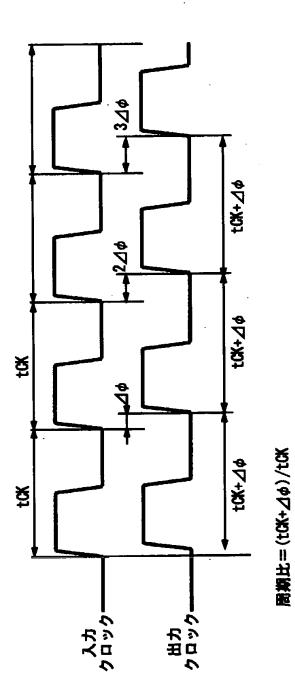

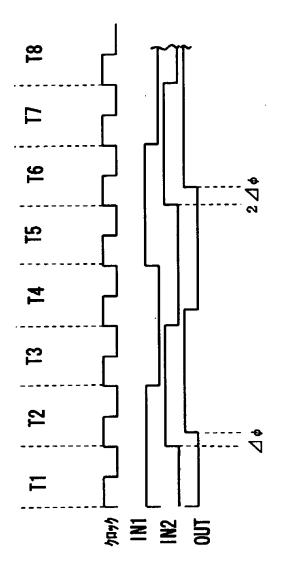

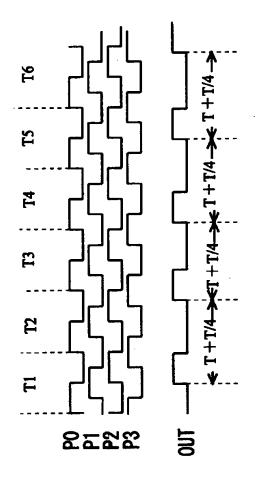

図2は、本発明の第1の実施例の動作原理を説明するためのタイミングチャートである。図2を参照すると、

クロックサイクル1の入力クロックの立ち上がりエッジに対する、出力クロッ

特2000-22120

クの位相差は0、

クロックサイクル2の入力クロックの立ち上がりエッジに対する、出力クロッ クの位相差は、ΔΦ、

クロックサイクル3の入力クロックの立ち上がりエッジに対する、出力クロッ クの位相差は、2ΔΦ、

…となる。

[0032]

出力クロックの周期は、 $tCK + \Delta \Phi \geq x$ り、周期tCKの入力クロックの周 波数 $f = 1 / tCK \geq R$ 、周波数 $f' = 1 / (tCK + \Delta \Phi)$ に周波数変換してお り、クロック周期を、入力クロック周波数の整数比以外(非整数)の値(=1+  $\Delta \Phi / tCK$ )で、周波数変換している。

[0033]

図2において、出力クロックと入力クロックを入れ替えたものが、制御回路1 02を減算回路とデコーダで構成した場合のタイミング動作となる。制御回路1 02を減算回路で構成した場合、クロックサイクル毎に、入力クロックの立ち上 がりエッジに対する、出力クロックの位相差は、- ΔΦ、- 2ΔΦ、…となる。

[0034]

次に本発明の第2の実施例について説明する。図3は、本発明の第2の実施例 の構成を示す図である。図3を参照すると、本発明の第2の実施例は、入力クロ ックを分周する分周回路103と、制御回路104と、位相調整回路101とを 備えている。分周回路103は、入力クロックを入力して分周する。

[0035]

制御回路104は、初期値0から、コード信号m(m=1、2、3、…)を、 入力クロックを入力するたびにインクリメント(0、m、2m、3m、…)する 加算回路と、該値をデコードし、該値に対応する選択信号を位相調整回路101 に出力するデコーダを備えている。

[0036]

位相調整回路101は、単位位相差を△Φとしたとき、入力クロック毎に、入 カクロックのエッジに対して、制御回路104からの選択信号に基づき、0、m

出証特2001-3028385

特2000-22120

$\Delta \Phi$ 、2m $\Delta \Phi$ 、3m $\Delta \Phi$ 、…、(n-1)m $\Delta \Phi$ 、nm $\Delta \Phi$ 、…の位相差の信 号を出力する。ただし、単位位相差 $\Delta \Phi$ がtCK/nのとき、nm $\Delta \Phi$ は位相差 0と等価である。

[0037]

周期 t C K の入力クロックの周波数 f = 1 / t C K を、周波数 f' = 1 / (t C K +  $\Delta \Phi$ ) に変換しており、出力クロックの周期を、t C K +  $\Delta \Phi$ となり、クロック周期を整数比以外の値で変更可能としている。

[0038]

本発明の第2の実施例においても、制御回路102を減算回路とデコーダで構 成してもよいことは勿論である。

[0039]

次に本発明の第3の実施例について説明する。図4は、本発明の第3の実施例 の構成を示す図である。図4を参照すると、本発明の第3の実施例は、多相クロ ック発生回路201と、セレクタ202と、セレクタ202への選択信号を供給 する制御回路203とを備えている。

[0040]

多相クロック発生回路201から出力される、例えばn相の第1~第nのクロ ック(位相が隣接するクロックのタイミング(位相)差ΔΦ=tCK/n)に対 して、制御回路203からの制御のもと、セレクタ202で、第1のクロックか ら第nのクロックを巡回的に選択することで、例えば、

クロックサイクル1では第1のクロックを選択し、入力クロックの立ち上がり エッジに対する出力クロックの位相差は0、

クロックサイクル2では第2のクロックを選択し、入力クロックの立ち上がり エッジに対する、出力クロックの位相差は、ΔΦ、

クロックサイクル3では第3のクロックを選択し、入力クロックの立ち上がり エッジに対する、出力クロックの位相差は、2ΔΦ、

…となる。

[0041]

出力クロックの周期は、 t C K + Δ Φ となり、周期 t C K の入力クロックの周

特2000-22120

波数 $f = 1 / t C K \delta$ 、周波数 $f' = 1 / (t C K + \Delta \Phi)$ に変換しており、クロック周期を、整数比以外の値(=1+ $\Delta \Phi / t C K$ )で変更可能としている。

[0042]

上記した本発明の実施例についてさらに詳細に説明する。以下では、本発明の 特徴の一つをなすタイミング差分割回路(インターポレータ)に関する説明の順 序の関係を考慮して、図4の回路構成から、その詳細を説明する。

[0043]

図5は、図4の多相クロック発生回路201の構成の一例を示す図である。図 6は、本発明の一実施例として、4相クロックを生成するための多相クロック発 生回路201として、逓倍用インターポレータの構成の具体例を示す図である。

[0044]

図5に示すように、4相クロック発生回路は、入力クロック1を4分周し、4 相クロックQ1~Q4を出力する1/4分周回路2と、n段縦続接続された4相 クロック逓倍回路51~5nと、周期検知回路6と、を備えている。最終段の4 相クロック逓倍回路5nからは、2n逓倍された4相クロックQn1~Qn4が 出力される。なお、4相クロック逓倍回路の段数nは任意である。

[0045]

1/4分周回路2は、入力クロック1を1/4分周して、4相クロックQ1、 Q2、Q3、Q4を生成し、このクロックQ1、Q2、Q3、Q4を4相クロッ ク逓倍回路51で逓倍した4相クロックQ11、Q12、Q13、Q14を生成 し、同様にして、4相クロック逓倍回路5nから、2n逓倍した4相クロックQ n1、Qn2、Qn3、Qn4を得る。

[0046]

周期検知回路6は、固定段数のリングオシレータと、カウンタから構成され、 クロック1の周期中、リングオシレータの発振回数をカウンタでカウントし、カ ウント数に応じて制御信号7を出力し、4相クロック逓倍回路5内の負荷を調整 する。この周期検知回路6により、クロック周期の動作範囲、デバイスの特性ば らつきが解消される。

[0047]

特2000-22120

図6(a)は、図5に示した4相クロック逓倍回路5の構成の一例を示す図で ある。なお、図5に示した4相クロック逓倍回路51~5nは、いずれも同一構 成とされる。図6(a)を参照すると、この4相クロック逓倍回路5は、8組の タイミング差分割回路4a1~4a8と、8個のパルス補正回路4c1~4c8 と、4組の多重化回路4b1~4b4から構成されている。図6(b)は、パル ス幅補正回路4cの構成を示す図であり、第2の入力をインバータ17で反転し た信号と、第1の入力を入力とするNAND回路16からなる。図6(c)は、 多重化回路4bの構成を示す図であり、2入力NAND回路18からなる。

[0048]

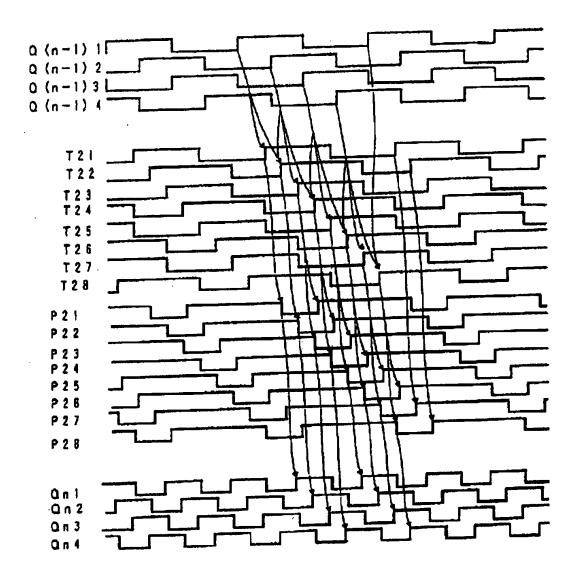

図7は、図6に示した4相クロック逓倍回路5のタイミング動作を示す信号波 形図である。クロックT21の立ち上がりは、クロックQ(n-1)1の立ち上 がりからタイミング差分割回路4a1の内部遅延分の遅れで決定され、クロック T22の立ち上がりは、クロックT22の立ち上がりは、クロックQ(n-1) 1の立ち上がりとクロックQ(n-1)2の立ち上がりのタイミングのタイミン グ差分割回路4a2でのタイミング分割と内部遅延分の遅れで決定され、以下同 様にして、クロックT26の立ち上がりはクロックQ(n-1)3の立ち上がり とクロックQ(n-1)4の立ち上がりのタイミングのタイミング差分割回路4 a6でのタイミング分割と内部遅延分の遅れで決定され、クロックT27の立ち 上がりはクロックQ(n-1)4の立ち上がりのタイミングのタイミング差分割 回路4a7での内部遅延分の遅れで決定され、クロックT27の立ち 上がりはクロックQ(n-1)4の立ち上がりのタイミングのタイミング差分割 マックQ(n-1)4の立ち上がりのタイミングのタイミングのタイミング差分割

【0049】

クロックT21とT23はパルス幅補正回路4 c1に入力され、パルス幅補正 回路4 c1では、クロックT21で決定される立ち下がりエッジ、クロックT2 3で決定される立ち上がりエッジを有するパルスP21を出力する。同様の手順 でパルスP22~P28が生成され、クロックP21~P28は位相が45度ず つずれたデューティ25%の8相のパルス群となる。このクロックP21と位相

特2000-22120-

が180度ずれたクロックP25は、多重化回路4b1で多重化反転され、デュ ーティ25%のクロックQn1として出力される。

[0050]

同様にして、クロックQn2~Qn4が生成される。クロックQn1~Qn4 は、位相が90度ずつずれたデューティ50%の4相のパルス群となり、クロッ クQn1~Qn4の周期は、クロックQ(n-1)1~Q(n-1)4からクロ ックQn1~Qn4を生成する過程で、周波数が2倍に逓倍される。

[0051]

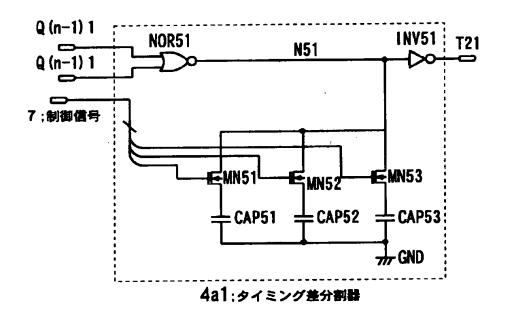

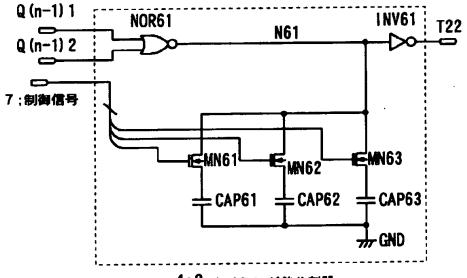

図8(a)、及び図8(b)は、図7に示したタイミング差分割回路4a1、 4a2の構成の一例をそれぞれ示す図である。これらの回路は互いに同一構成と されており、二つの入力が、同一信号であるか、隣り合う二つの信号が入力され るかが相違している。すなわち、タイミング差分割回路4a1では、同一入力Q (n-1)1が2入力NOR51に入力され、タイミング差分割回路4a2では Q(n-1)1とQ(n-1)2が2入力NOR61に入力されていること以外 、タイミング差分割回路は同一構成である。2入力NOR51、61は、周知の ように、電源VDDと出力端の間に直列に接続され、入力信号IN1、IN2を ゲートにそれぞれ入力する二つのPチャネルMOSトランジスタと、出力端とグ ランド間に並列に接続され、入力信号IN1、IN2をゲートにそれぞれ入力す る二つのNチャネルMOSトランジスタからなる。

【0052】

2入力NOR51 (NOR61)の出力ノードである内部ノードN51 (N6 1)は、インバータINV51 (INV61)の入力端に接続され、内部ノード とグランド間には、NチャネルMOSトランジスタMN51と容量CAP51を 直列接続した回路、NチャネルMOSトランジスタMN52と容量CAP52を 直列接続した回路を、並列に接続し、各NチャネルMOSトランジスタMN53と容量CAP53を 直列接続した回路を、並列に接続し、各NチャネルMOSトランジスタMN51 、MN52、MN53のゲートには、周期検知回路6からの制御信号7がそれぞ れ接続され、オン・オフ制御される。NチャネルMOSトランジスタMN51、 MN52、MN53のゲート幅と容量CAP51、CAP52、CAP53は、

特2000-22120

そのサイズ比が、例えば1:2:4とされており、周期検知回路6(図5参照) から出力される制御信号7に基づき、共通ノードに接続される負荷を、8段階に 調整することで、クロック周期が設定される。

[0053]

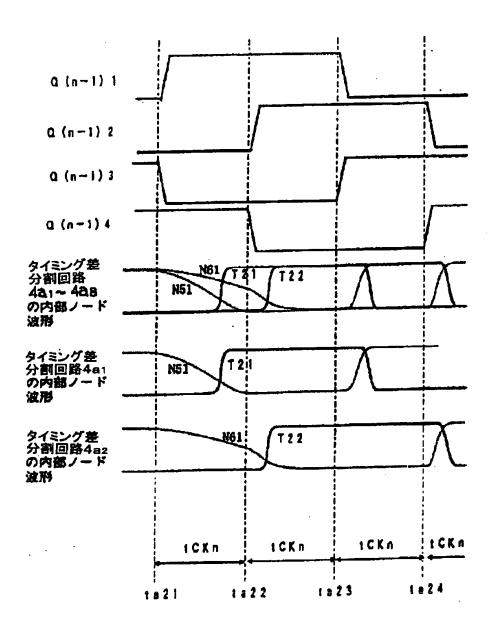

図9は、図8に示したタイミング差分割回路4a1、4a2の動作を説明する ためのタイミング図である。

[0054]

タイミング差分割回路4 a 1 については、クロックQ(n-1) 1の立ち上が りエッジにより、ノードN51の電荷がNOR51のNチャネルMOSトランジ スタを介して引き抜かれ、ノードN51の電位がインバータINV51のしきい 値に達したところで、インバータINV51の出力であるクロックT21が立ち 上がる。インバータINV51のしきい値に達したところまで引き抜く必要のあ るノードN51の電荷をCV(ただし、Cは容量値、Vは電圧)とし、NOR5 1のNチャネルMOSトランジスタによる放電電流をIとすると、クロックQ( n-1)1の立ち上がりから、CVの電荷量を、電流値2Iで放電することにな り、その結果、時間CV/2Iが、クロックQ(n-1)1の立ち上がりエッジ から、クロックT21の立ち上がりまでのタイミング差(伝搬遅延時間)を表し ている。クロックQ(n-1)1がLowレベルのとき、2入力NOR51の出 カ側ノードN51がHighに充電され、インバータINV51の出力クロック T21はLowレベルとなる。

[0055]

タイミング差分割回路4 a 2については、クロックQ(n-1)1の立ち上が りエッジから時間tCKn(tCKn=クロック周期)後の期間、ノードN61 の電荷がNOR61に引き抜かれ、時間tCKn後、クロックQ(n-1)2の 立ち上がりエッジから、ノードN61の電位がインバータINV61のしきい値 に達したところで、クロックT22のエッジが立ち上がる。ノードN61の電荷 をCVとし、2入力NOR61のNMOSトランジスタの放電電流をIとすると 、クロックQ(n-1)1の立ち上がりからCVの電荷量をtCKnの期間Iの 電流で放電し、残りの期間を電流2Iで引き抜く結果、時間、

出証特2001-3028385

特2000-22120

$t C K n + (C V - t C K n \cdot I) / 2I$

$= C V / 2 I + t C K n / 2 \qquad \cdots (1)$

が、クロックQ(n-1)1の立ち上がりエッジからクロックT22の立ち上 がりエッジのタイミング差を表している。

[0056]

すなわち、クロックT22とクロックT21の立ち上がりのタイミング差は、 tCKn/2となる。

[0057]

クロックQ (n-1) 1とQ (n-1) 2がともにLowレベルとなり、2入 カNOR61の出力側ノードN61が、NOR61のPMOSトランジスタを介 して電源からHighレベルに充電された場合、クロックT22が立ち上がる。

[0058]

図7のクロックT22~T28についても同様とされ、クロックT21~T2 8の立ち上がりのタイミング差はそれぞれtCKn/2となる。

[0059]

パルス幅補正回路4 c 1 ~ 4 c 8 (図6参照)は、位相が4 5 度ずつずれたデ ユーティ2 5 % の 8 相のパルス群 P 2 1 ~ P 2 8 (図 7 参照)を生成する。

[0060]

多重化回路4 b 1 ~ 4 b 4 (図6参照)は、位相が90度ずつずれたデューティ50%の4相のパルス群Qn1~Qn4 (図7参照)を生成する。

[0061]

図7のクロックQn1~Qn4が、図4の4相クロック発生回路201から出 力されるものとすると、Qn1~Qn4を入力するセレクタ203は、制御回路 202からの選択信号の制御のもと、クロックQn1、Qn2、Qn3、Qn4 の順に選択して出力する。クロックQn1~Qn4の周期をTとするとすると、 周期T(1+1/4)のクロックがセレクタ203から出力される。

[0062]

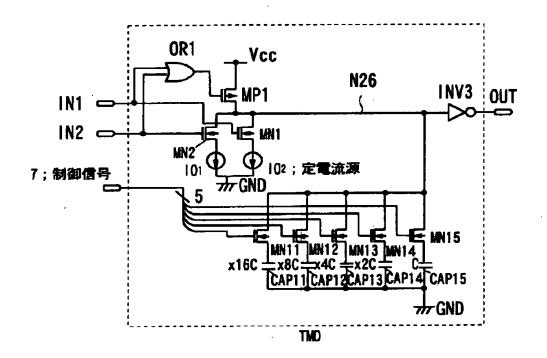

図10は、図6等の4相クロック逓倍回路に用いられるタイミング差分割回路 の別の例を示す図である。図10を参照すると、第1、第2の入力信号IN1、

特2000-22120-7

IN2を入力とする論理和回路OR1と、電源VCCと内部ノードN26間に接 続され、論理和回路OR1の出力信号をゲート入力とするPチャネルMOSトラ ンジスタMP1と、内部ノードN26の電位を反転出力するインバータINV3 と、内部ノードN26にドレインが接続され、第1の入力信号IN1、第2の入 力信号IN2をそれぞれゲートに入力とし、ソースが定電流源I<sub>0</sub>に接続される NチャネルMOSトランジスタMN1、MN2を備えている。内部ノードN26 と接地間には、NチャネルMOSトランジスタよりなるスイッチ素子MN11~ MN15と、容量CAP11~CAP15が接続され、NチャネルMOSトラン ジスタよりなるスイッチ素子MN11~MN15の制御端子(ゲート端子)には 、図8を参照して説明したタイミング差分割回路と同様、図5の周期検知回路6 から出力される制御信号7が接続され、制御信号7の値により、NチャネルMO SトランジスタMN11~MN15がオン・オフ制御され、内部ノードN26に 付加する容量値が決められる。容量CAP11~CAP15の容量値の比は、1 6:8:4:2:1とされ、NチャネルMOSトランジスタMN11~MN15 のW(ゲート幅)/L(ゲート長)比は、16:8:4:2:1とされる。

[0063]

第1、第2の入力信号IN1、IN2がLowレベルのとき、論理和回路OR 1の出力はLowレベルとなり、PチャネルMOSトランジスタMP1がオン( 導通)し、これにより内部ノードN26が電源電位に充電されインバータINV 3の出力はLowレベルとされる。

[0064]

第1、第2の入力信号IN1、IN2の一方又は両方がHighレベルとなる と、論理和回路OR1の出力はHighレベルとなり、PチャネルMOSトラン ジスタMP1がオフし、内部ノードN26と電源Vccとの電源パスがオフし、 一方、NチャネルMOSトランジスタMN1とMN2の一方又は両方がオンして 内部ノードN26が放電されて、内部ノードN26の電位が電源電位から下がり 始め、インバータINV3のしきい値以下に下がった場合、インバータINV3 の出力はLowレベルから立上がってHighレベルとなる。

[0065]

特2000-22120-

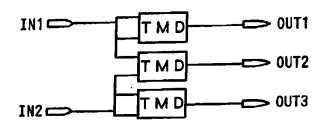

図11は、図8、図10に示したタイミング差分割回路(TMD)の動作を説 明するための図である。図10(a)を参照すると、3つのタイミング差分割回 路(TMD)において、第一のタイミング差分割回路(TMD)は、その二入力 に、同一の入力信号IN1が入力され出力信号OUT1を出力し、第2のタイミ ング差分割回路(TMD)には入力信号IN1、IN2が入力され出力信号OU T2を出力し、第三のタイミング差分割回路(TMD)は、その2入力に、同一 の入力信号IN2が入力され出力信号OUT3を出力する。このうち、入力信号 IN1、IN2を入力し出力信号OUT2を出力する第二のタイミング差分割回 路(TMD)が、図8(b)のタイミング差分割回路の構成に対応している。ま たIN1を共通に入力するタイミング差分割回路(TMD)、IN2を共通に入 力するタイミング差分割回路(TMD)は、図8(a)において、同一信号を入 力する構成とされ、図6のタイミング差分割回路4 a 2等の構成に対応している

[0066]

α

図11(b)は、タイミング差Tの入力信号IN1、IN2を入力した第一乃 至第三のタイミング差分割回路の出力信号OUT1~OUT3の出力と、第一乃 至第三のタイミング差分割回路の内部ノードの変化A1~A3を示している。説 明を容易とするため、内部ノードは電位Oから充電され、しきい値Vtを超えた とき、出力信号がLowからHighレベルに変化(立上がる)するものとする

[0067]

図11(b)を参照すると、入力信号IN1と入力信号IN2間には、タイミング差(T)があり、第一のタイミング差分割回路(TMD)は遅延時間t1の 出力信号OUT1を出力し、第三のタイミング差分割回路(TMD)は遅延時間 t3の出力信号OUT3を出力し、第二のタイミング差分割回路(TMD)は、 遅延時間t2の出力信号OUT2を出力し、遅延時間t2は、遅延時間t1とt 3を分割(内分)した値とされている。

[0068]

t 1 = C V / 2 I,

特2000-22120

t 2 = T + (CV - IT) / (2I)

$= T / 2 + C V / 2 I \cdots (2)$

とされる。

[0069]

また、

t 3 = T + C V / 2 I とされる(図11(c)参照)。ただし、内部ノードが 入力端に接続されるバッファ回路(インバータ)のしきい値を超えるまでに放電 する電荷をC V とする。

[0070]

次に、本発明の実施例の位相調整回路101等で用いられ、入力する二つの信 号のタイミング差を分割する内分比が可変に設定可能とされるインターポレータ の構成について説明する。

[0071]

図12は、図1の位相調整回路101等を構成する、タイミング差の内分比が 可変に設定可能なインターポレータの回路構成の一例を示す図である。図12を 参照すると、このインターポレータは、ソースが電源Vccに接続され、ドレイ ンが内部ノードN31に接続され、第1、第2の入力信号IN1、IN2を入力 とする否定論理積回路NANDO1の出力信号をゲートに入力するPチャネルM **OSトランジスタMP1と、内部ノード電位としきい値電圧の大小関係が変化し** た時に、出力信号の論理値をスイッチングさせるインバータ回路INV3と、入 力信号IN1、IN2に入力端がそれぞれ接続されているインバータ回路INV 1、INV2と、内部ノードN31にドレインが共通接続され、ゲートがインバ ータ回路INV1の出力に接続される16個のNチャネルMOSトランジスタM N111~MN11116と、内部ノードN31にドレインが共通接続され、ゲート がインバータ回路INV2の出力に接続される16個のNチャネルMOSトラン ジスタMN12<sub>1</sub>~MN12<sub>16</sub>と、NチャネルMOSトランジスタMN11<sub>1</sub>~M N11<sub>16</sub>のソースにドレインが接続され、ソースが定電流源I<sub>0</sub>にそれぞれ接続 され、ゲートが制御回路(図1の制御回路102等)からの選択信号(PH)を 入力して反転するインバータ回路INV4の出力に接続され、オン・オフ制御さ

出証特2001-3028385

特2000-22120

れる16個のNチャネルMOSトランジスタ(スイッチ素子)MN21<sub>1</sub>~MN 21<sub>16</sub>と、NチャネルMOSトランジスタMN12<sub>1</sub>~MN12<sub>16</sub>のソースにド レインが接続され、ソースが定電流源I<sub>0</sub>にそれぞれ接続され、ゲートが制御回 路(図1の制御回路102等)からの選択信号(PH)に接続され、オン・オフ 制御される16個のNチャネルMOSトランジスタ(スイッチ素子)MN22<sub>1</sub> ~MN22<sub>16</sub>と、を備えている。

[0072]

さらに内部ノードN31と接地(GND)間には、容量Cが接続されている。 【0073】

入力信号IN1で、16並列のNチャネルMOSトランジスタのうちN個(た だし、Nは0~16、N=0はオンするものがない場合であり、Nは制御信号C で決定される)がオンし、時間T後に、入力信号IN2によって、(16-N) 個の並列のNチャネルMOSトランジスタがオンし、全体で、N+(16-N) =16個のNチャネルMOSトランジスタがオンする場合におけるタイミング差 の内分の動作について説明する。

[0074]

並列のNチャネルMOSトランジスタ1個に流れる電流はI(定電流源I<sub>0</sub>の 電流値)であり、インバータINV3の出力が反転するしきい値電圧をVとして 、しきい値電圧Vまでの電荷の変動量をCVとする。

【0075】

ここで、入力信号IN1、IN2がともにHighレベルとされ、NAND0 1の出力がLowレベルとされ、PチャネルMOSトランジスタMP1を介して 、内部ノードN31は、電源側から充電された状態にあるものとする。この状態 から、入力信号IN1、IN2がLowレベルに立ち下がる場合について説明す る。

[0076]

まずN=16の場合、入力信号IN1で、16並列のNチャネルMOSトラン ジスタMN11<sub>1</sub>~MN11<sub>16</sub>のうち16個がオンし、時間T後に、入力信号I N2によって16個並列配置されるNチャネルMOSトランジスタMN12<sub>1</sub>~

特2000-2212

$MN12_{16}$ がいずれもオフとされる((16-N)=0)。したがって、N=1 6の場合、定電流源 $I_0$ の電流をIとして、入力信号IN1がLowレベルになってから、インバータINV3の出力が反転するまでの時間T(16)は、

T (16) =  $CV / (16 \cdot I)$  ...(3)

[0077]

N=n(n<16)の場合(Nは制御信号Cで設定される)、入力信号IN1 がLowレベルになってから時間T(ただし、Tは入力信号IN1とIN2の立 ち下がりエッジのタイミング差)の間、入力信号IN1の反転信号をゲートに入 力とするn個のNチャネルMOSトランジスタがオンし、n・I・Tの電荷が放 電され、つづいて、入力信号IN2がLowレベルとなることで、入力信号IN 2の反転信号をゲートに入力とする16-n個のNチャネルMOSトランジスタ がオンし、全体で、16のNチャネルMOSトランジスタがオンし、内部ノード N31に残存する電荷(CV-n・I・T)を、(16・I)で放電した時点( 時間T')で、インバータINV3の出力が反転する(HighレベルからLo wレベルとなる)。時間T'は、(CV-n・I・T)/(16・I)で与えら れる。

[0078]

したがって、入力信号IN1がLowレベルになってから、インバータINV 3の出力が反転するまでの時間T(n)は、

$T(n) = (CV - n \cdot I \cdot T) / (16 \cdot I) + T$

$=CV / (16 \cdot I) - (n / 16) T + T$

=T (16) + ((16-n) / 16) · T ...(4)

で与えられる。

[0079]

nの値によって、入力信号IN1とIN2のタイミング差Tを、16等分した 位相の出力信号が得られる。すなわち、制御信号の設定により、nを可変するこ とで、入力信号IN1とIN2の間のタイミング差を分解能1/16で分割した 任意の位相の出力信号が得られる。このようなインターポレータを「16刻みの インターポレータ」ともいう。一般に、インターポレータを、M刻み(Mは任意

出証特2001-3028385

特2000-22120-

の正整数)とする場合、NチャネルMOSトランジスタMN11、MN12、M N21、MN22がそれぞれM個並列配置される。

[0080]

このインターポレータの入力IN1、IN2に、例えばタイミング差が1クロ ック周期tCKの二つの信号を入力し、入力クロック毎に、入力IN1から、タ イミング差0、tCK/16、2tCK/16、…を出力することで、tCK( 1+1/16)のクロック周期の信号を生成することができる。

[0081]

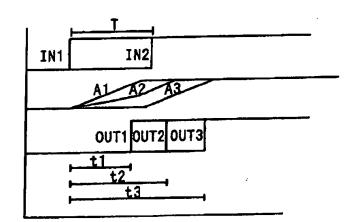

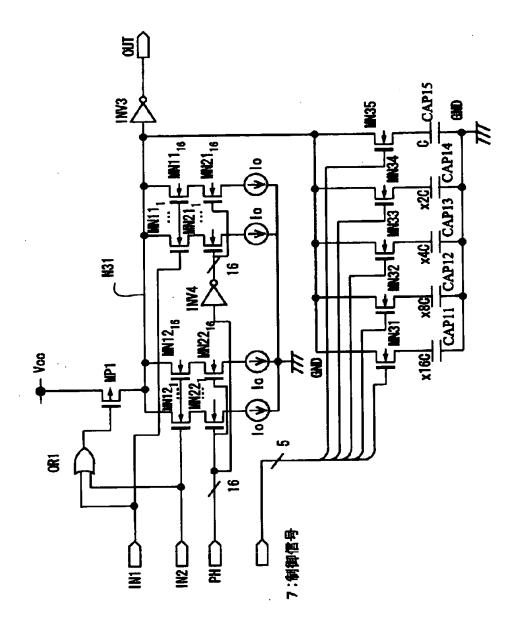

図13は、図1の位相調整回路101等を構成するインターポレータの回路構 成を示す図であり、図12に示した構成において、内部ノードN31と接地間に 、NチャネルMOSトランジスタよりなるスイッチ素子と容量とからなる直列回 路が、複数並列接続され(スイッチ素子MN21~MN35、容量CAP11~ 15)、スイッチ素子MN11~MN15の制御端子に接続する制御信号(容量 選択周波数調整信号)7にて、内部ノードに付加する容量が決められる。容量C AP11~15は、容量値がC、2C、4C、8C、16Cとされ、スイッチ素 子MN11~15の周期制御信号7の値によって、内部ノードに付加される容量 値が可変される。周期制御信号7は外部から設定され、例えば図5に示した周期 検知回路6から供給される制御信号7が用いられる。

[0082]

図12に示したインターポレータは、入力信号IN1、IN2がともにHig hレベルのとき内部ノードN31が電源電位に充電され、入力信号IN1、IN 2がHighレベルからLowレベルへの立下りの遷移に対して、内部ノードN 31が放電され、出力信号が、LowレベルからHighレベルに立ち上がるも のであるが、これ以外に、入力信号がLowレベルからHighレベルの立ち 上がり遷移に対して、出力信号が、LowレベルからHighレベルに立ち上が る構成としてもよい。入力信号IN1、IN2がHighレベルからLowレベ ルへの立下りの遷移に対して、出力信号が、HighレベルからLowレベルに 立ち下がる論理とするには、反転型バッファであるインバータINV3を、正転 バッファ回路とすればよい。

特2000-2212

[0083]

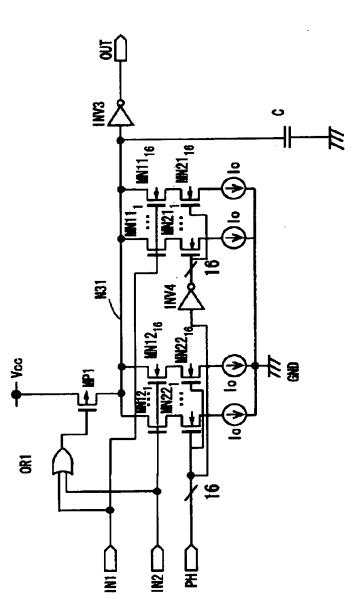

図14は、図1の位相調整回路101等を構成するインターポレータの別の回 路構成を示す図である。図14を参照すると、ソースが電源に接続され、ドレイ ンが内部ノードN31に接続され、第1、第2の入力信号IN1、IN2を入力 とする論理和回路OR1の出力信号をゲートに入力するPチャネルMOSトラン ジスタMP1と、内部ノード電位としきい値電圧の大小関係が変化した時に、出 力信号の論理値をスイッチングさせるインバータ回路INV3と、内部ノードN 31にドレインが共通接続され、ゲートが入力信号 IN1に共通接続される16 個のNチャネルMOSトランジスタMN11110K、内部ノードN3 1にドレインが共通接続され、ゲートが入力信号 IN2に共通接続される16個 のNチャネルMOSトランジスタMN12<sub>1</sub>~MN12<sub>16</sub>と、NチャネルMOS トランジスタMN1111~MN1116のソースにドレインが接続され、ソースが 定電流源 I<sub>0</sub>にそれぞれ接続され、ゲートが制御回路(図1の制御回路102等 )からの選択信号(PH)を入力して反転するインバータ回路INV4の出力に 接続され、オン・オフ制御される16個のNチャネルMOSトランジスタ(スイ ッチ素子) MN 2 1  $_1$ ~MN 2 1  $_{16}$ と、NチャネルMO SトランジスタMN 1 2  $_1$ ~MN12<sub>16</sub>のソースにドレインが接続され、ソースが定電流源I<sub>0</sub>にそれぞれ 接続され、ゲートが制御回路(図1の制御回路102等)からの選択信号(PH )に接続され、オン・オフ制御される16個のNチャネルMOSトランジスタ( スイッチ素子) MN 2 2 1~MN 2 2 16と、を備えている。

[0084]

図15は、図14に示した構成において、内部ノードN31と接地間に、NチャネルMOSトランジスタよりなるスイッチ素子と容量とからなる直列回路が、 複数並列接続され(スイッチ素子MN21~MN35、容量CAP11~15) 、スイッチ素子MN11~MN15の制御端子に接続する制御信号(容量選択周 波数調整信号)7にて、内部ノードに付加する容量が決められる。容量CAP1 1~15は、容量値がC、2C、4C、8C、16Cとされ、スイッチ素子MN 11~15の周期制御信号7の値によって、内部ノードに付加される容量値が可 変される。周期制御信号7は外部から設定され、例えば図5に示した周期検知回

出証特2001-3028385

特2000-22120

路6から供給される制御信号が用いられる。

[0085]

次に本発明のさらに別の実施例について説明する。図16は、本発明の第4の 実施例の構成を示す図であり、図3に示した分周回路103と、位相調整回路1 01と、制御回路102とを備えたクロック制御回路において、位相調整回路1 01を、図12乃至図15に示したインターポレータで構成したものである。

[0086]

分周回路103で分周した信号をデータ端子に入力し、クロック信号をクロッ ク端子に入力する第1のD型フリップフロップ113でラッチしたクロック信号 と、該クロック信号を第2のD型フリップフロップ114でラッチしたクロック 信号を第1、第2の入力IN1、IN2としてインターポレータ110に入力し 、インターポレータ110は、第1、第2の入力IN1、IN2のタイミング差 (クロックCLKの周期tCK)を、加算回路112と、加算回路112の出力 をデコードするデコーダ111からなる制御回路102より出力される制御信号 (選択信号)で設定される、内分比で分割した出力信号OUTを出力する。

[0087]

図17は、図16に示した回路の動作の一例を説明するためのタイミング波形 図である。分周回路103は、クロックを1/4分周しており、インターポレー タ110は、図14に示した回路よりなり、入力信号IN1、IN2がともにL owレベルのとき内部ノードを充電し、入力信号IN1、IN2がLowレベル からHighレベルへ遷移する立ち上がりに対して、内部ノードN31が放電さ れ、インバータ回路INV3を介して、入力信号IN1、IN2のタイミング差 (クロック周期tCK)を、制御信号PHで設定される内分比で分割したタイミ ングで立ち上がる出力信号OUTが出力される。

[0088]

図17を参照すると、クロックサイクルT2のクロックの立ち上がりエッジか ら時間Δφ遅れて、インターポレータ110から信号OUTがLowレベルから Highレベルに立ち上がり、クロックサイクルT4で、インターポレータに入 力される入力信号IN1、IN2がともにLowレベルとなり、内部ノードN3

特2000-2212

1が電源電位に充電されて出力OUTはLowレベルとなり、インターポレータ のNチャネルMOSトランジスタMN21、MN22のゲートに供給される制御 信号PHの値が切り替えられ、クロックサイクルT6のクロックの立ち上がりエ ッジから時間2Δφ遅れて、インターポレータ110から信号OUTがLowレ ベルからHighレベルに立ち上がる。この場合、インターポレータ110から 出力される出力クロックの周期は、4tCK+Δφとなる。

[0089]

このように、分周クロックの一クロックサイクル内の所定のタイミングで、イ ンターポレータ110(図12乃至図15参照)のNチャネルMOSトランジス タMN21、22に供給する制御信号(図1の選択信号)の設定値を可変させる ことで、分周クロックサイクルベースで、出力クロックの入力クロックのエッジ に対するタイミング(位相差)を可変させ、周波数の変換を行う、ことができる

[0090]

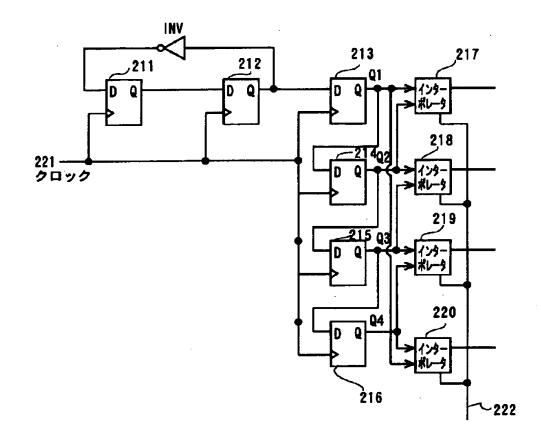

次に本発明のさらに別の実施例について説明する。図18は、本発明の第5の 実施例の構成を示す図であり、図1に示した位相調整回路101に、図12乃至 図15のインターポレータを用いて構成した一例を示す図である。図18を参照 すると、2段直列に接続され、後段の出力をインバータINVで反転した信号が 前段のデータ端子Dに帰還入力されるD型フリップフロップ211、212と、 D型フリップフロップ212の出力を入力とし、直列に接続されシフトレジスタ を構成する第1の乃至第4D型フリップフロップ213~216と、第1、第2 のフリップフロップ213、214の出力Q1、Q2を入力としそのタイミング 差Tを分割した遅延時間の信号を出力する第1のインターポレータ217と、第 2、第3のフリップフロップ214、215の出力Q2、Q3を入力としそのタ イミング差Tを分割した遅延時間の信号を出力する第2のインターポレータ21 8と、第3、第4のフリップフロップ215、216の出力Q3、Q4を入力と しそのタイミング差Tを分割した遅延時間の信号を出力する第3のインターポレ ータ219と、第4、第1のフリップフロップ216、213の出力Q4、Q1 を入力としそのタイミング差Tを分割した遅延時間の信号を出力する第4のイン

特2000-22120-

ターポレータ220と、を備えている。第1乃至第4のインターポレータ217 ~220には、タイミング差の内分比を設定する制御信号222が不図示の制御 回路から供給される。

[0091]

第1乃至第4のインターポレータ217~220に供給される制御信号222 の値は、クロック毎に切り替えることなく、固定値としてもよい。

[0092]

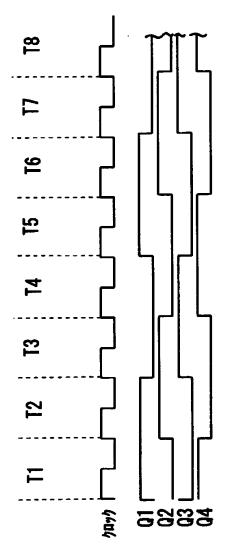

図19は、図18に示した回路の動作の一例を説明するための図である。図1 9を参照すると、第1のインターポレータ217は、信号Q1、Q2のタイミン グ差tCKを分割した出力信号(クロックサイクルT2のクロックの立ち上がり エッジからタイミング差ムφ)の信号を出力し、第2のインターポレータ218 は、信号Q2、Q3のタイミング差tCKを分割した出力信号(クロックサイク ルT3のクロックの立ち上がりエッジからタイミング差2Δφ)の信号を出力し 、第3のインターポレータ219は、信号Q3、Q4のタイミング差tCKを分 割した出力信号(クロックサイクルT4のクロックの立ち上がりエッジからタイ ミング差3Δφ)の信号を出力し、第4のインターポレータ220は、信号Q4 、Q1のタイミング差tCKを分割した出力信号(クロックサイクルT5のクロ ックの立ち上がりエッジからタイミング差4Δφ=クロックサイクルT6の始ま る)の信号を出力する。この場合、インターポレータからは、入力クロック(ク ロック周期tCK)に対して、周期tCK(1+1/4)のクロックが出力され る。

[0093]

第1乃至第4のインターポレータ217~220は、アプリケーションに応じ て、論理回路で演算した結果を出力してもよいし、あるいはセレクタで選択出力 する構成としてもよい。本発明は、例えばmBnB(mビットnビット)符号化 システムにおける、速度変換回路に用いて好適とされる。

[0094]

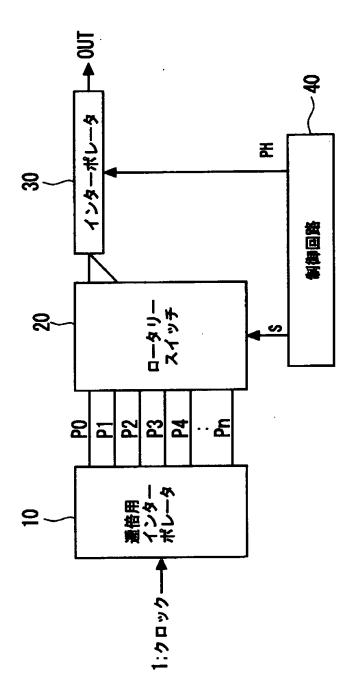

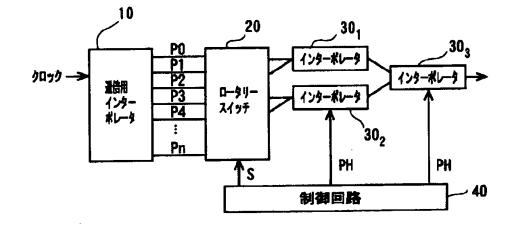

次に本発明のさらに別の実施例について説明する。図20は、本発明の第6の 実施例の構成を示す図である。図20を参照すると、逓倍用インターポレータ1

特2000-22120-

0と、スイッチ(ロータリースイッチ)20と、インターポレータ30(「微調 用インターポレータ」ともいう)と、制御回路40を備えている。

[0095]

逓倍用インターポレータ10は、入力クロック1から多相逓倍クロックP0~ Pnを生成する。逓倍用インターポレータ10は、図5に示した構成からなる。

[009<sup>·</sup>6]

スイッチ20は、多相通倍クロックP0~Pnの中の二つのクロックを選択し、 、 微調用インターポレータ30の二つの入力信号として供給する。

[0097]

制御回路40は、スイッチ20、及び、微調用インターポレータ30への制御 信号S、PH(インターポレータ30のNチャネルMOSトランジスタ21、2 2のゲートに供給される制御信号)を供給する。制御回路40は、クロック1を 入力とする加算回路(不図示)と、加算回路の出力をデコードして制御信号S、 PHを出力するデコーダ(不図示)を備えて構成されている。

[0098]

スイッチ20は、多相クロックP0~Pnのうち、制御回路40からの制御信 号Sに基づき、互いに隣合う、奇位相信号と偶位相信号を選択し、選択したクロ ック対をインターポレータ30に供給し、インターポレータ30は、制御回路4 0から出力される制御信号に基づき、二つの入力の位相差(タイミング差)を内 分した位相の信号を出力する。本実施例において、インターポレータ30は、図 12乃至図15等に示した構成とされる。

[0099]

図21は、インターポレータ30を、図15に示した回路で構成し、逓倍用イ ンターポレータ10(図5参照)が、4相の逓倍クロックP0~P3を生成出力 する場合の動作の一例を示す図である。

[0100]

ロータリスイッチ20は、多相クロックP0~P3のうち、例えば、(P0、 P1)、(P1、P2)、(P2、P3)、(P3、P0)、(P0、P1)、 …と巡回的に選択する。多相クロックの周期をTとすると、クロックサイクルT

特2000-22120

1で、スイッチ20はP0、P1を選択し、インターポレータ30はP0、P1 の立ち上がりをうけて出力信号OUTを出力し、サイクルT2で、スイッチ20 はP1、P2を選択し、インターポレータ30は、P1、P2の立ち上がりをう けて、前の出力信号OUTの立ち上がりエッジから時間T(1+1/4)のタイ ミングで出力信号OUTを出力し、以下、スイッチはP3、P4、つづいてP4 、P1を選択し、周期T(1+1/4)のクロックを出力する。

[0101]

図21に示す例では、インターポレータは、逓倍クロックの周期Tに対して周 期(1+1/4)T=5T/4のクロックを出力しており(周波数は4/5倍) 、逓倍用インターポレータ10が入力クロックを2m逓倍している場合、出力ク ロックの周波数は8m/5倍に変換される。

【0102】

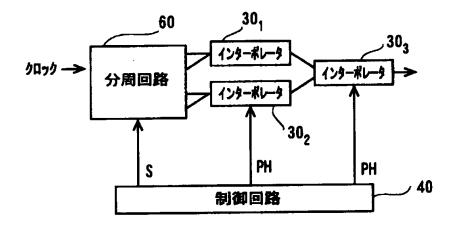

次に本発明のさらに別の実施例について説明する。図22は、本発明の第7の 実施例の構成を示す図である。図22を参照すると、本発明の第7の実施例は、 図20に示した構成の変形例であり、ロータリスイッチ20が二組のクロック対 を出力して、それぞれ第1、第2のインターポレータ30<sub>1</sub>、30<sub>2</sub>に供給し、二 つのインターポレータ30<sub>1</sub>、30<sub>2</sub>の出力を入力とする第3のインターポレータ 30<sub>3</sub>の出力から出力クロックを得る。

[0103]

本実施例において、第1乃至第3のインターポレータ30<sub>1</sub>~30<sub>3</sub>の各インタ ーポレータのタイミング差の内分比は制御回路40からの制御信号で可変される 構成としてもよい。あるいは、アプリケーションで求められるタイミング精度に 応じ、インターポレータ30<sub>1</sub>は、タイミング差の内分比が固定とされ、インタ ーポレータ30<sub>2</sub>とインターポレータ30<sub>3</sub>の内分比が制御回路40からの制御信 号で可変される構成としてもよい。さらには、インターポレータ30<sub>1</sub>とインタ ーポレータ30<sub>2</sub>をタイミング差の内分比を固定とし、最終段のインターポレー タ30<sub>3</sub>のみその内分比が制御回路40からの制御信号で可変される構成として もよい。

[0104]

本発明の第7の実施例は、図20に示した構成と比較して、微調用インターポ レータを多段構成としたことにより、タイミング差の内分比をさらに細かく設定 することができる。第2、第3のインターポレータ30<sub>2</sub>、30<sub>3</sub>を、図12乃至 図15に示した16等分インターポレータで構成した場合、1/256の分解能 でタイミング差を内分することができる。

[0105]

次に本発明の第8の実施例について説明する。図23は、図3に示した構成の 変形例を示す図であり、クロックを分周回路60で分周し、二つのクロック対を 出力して第1、第2のインターポレータ30<sub>1</sub>、30<sub>2</sub>に供給し、二つのインター ポレータ30<sub>1</sub>、30<sub>2</sub>の出力を入力とする第3のインターポレータ30<sub>3</sub>の出力 から出力クロックを得るようにしたものである。

[0106]

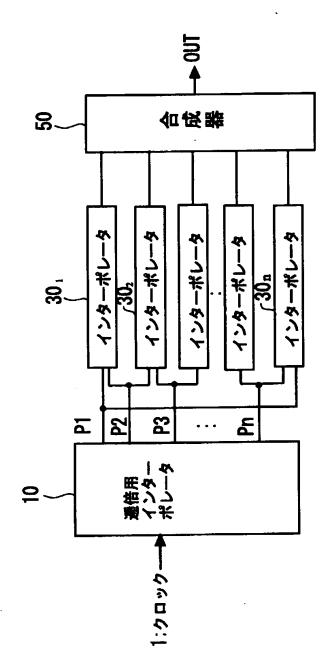

次に本発明の第9の実施例について説明する。図24は、本発明の第9の実施 例の構成を示す図である。図24を参照すると、本発明の第9の実施例は、図1 8に示した構成の変形例に対応するものであり、入力クロックに基づき、該入力 クロックを逓倍してなる互いに位相の異なる第1乃至第nのクロックP1~Pn (n相逓倍クロック)を生成する逓倍用インターポレータ10と、逓倍用インタ ーポレータ10から出力される、第1乃至第nのクロックP1~Pnについて、 互いに隣接する位相の二つのクロックを入力し、該二つのクロックのタイミング 差を、それぞれ互いに異なる所定の内分比で分割した信号をそれぞれ出力する第 1乃至第nのインターポレータ30<sub>1</sub>~30<sub>n</sub>と、第1乃至第nのインターポレー タ(微調用インターポレータ)30<sub>1</sub>~30<sub>n</sub>の出力を入力し、これらを多重化し て、一つの出力信号OUTとして出力する合成器50を備えている。

[0107]

第1乃至第nのインターポレータ $30_1 \sim 30_n$ は、図12乃至図15に示した 構成とされ、二つの入力信号のタイミング差Tを、m刻み( $n \leq m$ )で分割する ものとする。n相の多相逓倍クロックを生成する逓倍用インターポレータ10と 微調用インターポレータ30により、出力信号OUTとして、クロック周期(360度)を $n \times m$ 刻みで分割したタイミングを生成することができる。

[0108]

図24に示す例では、図18に示した構成と同様、n相のクロックのうち、隣 接するi番目とi+1番目のクロックPi、Pi+1(ただし、iは1~nの整数 、n+1番目のクロックは1番目のクロックP1となる)を入力とするインター ポレータ30<sub>i</sub>と、i-1番目とi番目のクロックPi-1、Piを入力とするイ ンターポレータ30<sub>i-1</sub>とは、タイミング差の内分比が異なるように設定されて おり、インターポレータ30<sub>i</sub>の方が、インターポレータ30<sub>i-1</sub>よりも、遅延時 間は大きくなる。

[0109]

第1乃至第nのインターポレータ30<sub>1</sub>~30<sub>n</sub>の出力を入力して多重化し、出 力信号OUTとして出力する合成器50は、例えば図6に示した、パルス幅補正 回路4 c、多重化回路4 bで構成される。

[0110]

図24に示した構成において、逓倍用インターポレータ10から出力される n 相の多相逓倍クロックから、M相のクロック(M逓倍クロック)を生成する構成 について説明する。この場合、インターポレータ30はM個並設される(ただし 、M≦N)。この場合も、i番目のインターポレータ30<sub>i</sub>には、隣接するi番 目とi+1番目のクロックPi、Pi+1(ただし、iは1~Mの整数、なお、 n+1番目のクロックは1番目のクロックP1となる)が入力される。各インタ ーポレータ30における二つの入力信号のタイミング差Tの分割位置を規定する 内分比として、

1番目のインターポレータ30<sub>1</sub>は、内分比m:M-m、

2番目のインターポレータ302は、内分比2m:M-2m、

3番目のインターポレータ303は、内分比3m:M-3m、

…という具合に、インターポレータの番号とともに、昇順に、順次、タイミン グ差Tの分割位置が、単位ステップmごとに、タイミング区間の先端側から後端 側にずらして設定される。なお、インターポレータの番号とともに、順次、タイ ミング差Tの分割位置を、単位ステップmごとに、タイミング区間の後端側から 先端側にずらして設定するようにしてもよい。この設定は、図12乃至図15を

出証特2001-3028385

参照して説明したように、インターポレータに供給される制御信号PHにて、インターポレータのNチャネルMOSトランジスタMN21、MN22のオン・オフを制御することで設定される。なお、本実施例において、各インターポレータの内分比は固定値とされる。

[0111]

M個のインターポレータ30の出力を多重化して一つの出力信号OUTとして 出力する合成器50からは、M逓倍のクロックを得ることができる。例えばn= 8、M=7の場合において、m=1とした場合、逓倍用インターポレータ10か ら出力される8相クロック(8相逓倍クロック)から、7相のクロックを生成す ることができる。そして、7相クロックを入力する合成器50からは、7逓倍ク ロックが出力される。

[0112]

図25は、16等分インターポレータの集積回路のレイアウトの一例を示す図 である。

[0113]

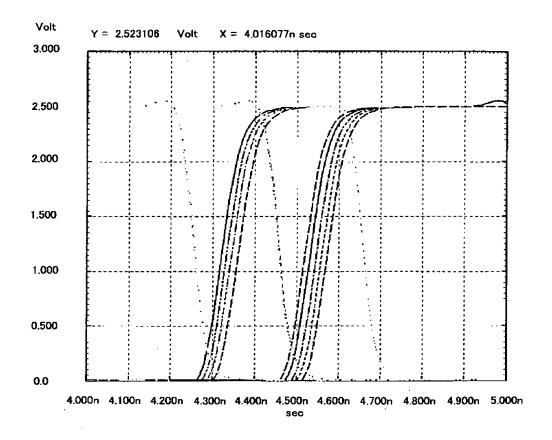

図26は、微調インターポレータを用いた位相調整回路のシミュレーション波 形を示す図であり、625MHzの位相差を16等分インターポレータで16等分 し、位相切り替わり部分の5位相分を表示したものである。微調位相差は12. 5psとなる。

[0114]

上記した本発明の実施例によれば、インターポレータを複数段備えた構成とす ることで、出力信号のタイミングエッジを10ピコ秒のオーダで制御することが できる。すなわち、本発明は、LSIにおけるクロック周波数変換回路、クロッ ク同期回路のみならず、測定装置、試験装置におけるパターン発生器、タイミン グ生成器等に適用され、例えば10ピコ秒のオーダの分解能で、オンザフライで タイミングが可変に設定されるLSIテスタのタイミング生成器等に用いて好適 とされる。

[0115]

また上記実施例において、例えば、図3及び図23等を参照して説明した分周

特2000-22120

回路と位相調整回路(位相微調用のインターポレータ)を備えた構成は、位相比 較器の位相差に応じた電圧を生成するチャージポンプと、ループフィルタと、ル ープフィルタの出力を制御電圧として入力するVCO(電圧制御発振器)と、V COの出力を分周した信号を該位相比較器に供給する分周回路を備えたPLL( 位相同期ループ)回路における分周回路に適用することができる。

[0116]

【発明の効果】

以上説明したように、本発明によれば、簡易な構成により、高精度に、非整数 の周波数変換を行うことができる、という効果を奏する。

[0117]

その理由は、本発明においては、クロックを入力とする位相調整回路から出力 される信号の位相を、クロック毎に、単位位相差、加算又は減算する構成とした ためである。

[0118]

また本発明によれば、帰還系を備えず、帰還系特有のジッタがなく、高速なク ロック同期を可能としている。

【図面の簡単な説明】

【図1】

本発明の第1の実施例の構成を示す図である。

【図2】

本発明の第1の実施例の動作を説明するためのタイミング図である。

【図3】

本発明の第2の実施例の構成を示す図である。

【図4】

本発明の第3の実施例の構成を示す図である。

【図5】

本発明の第3の実施例の多相クロック生成回路の構成の一例を示す図である。

【図6】

図5の4相クロック逓倍回路の構成の一例を示す図である。

出証特2001-3028385

特2000-22120

【図7】

図6の4相クロック逓倍回路の動作を説明するためのタイミング図である。

【図 8】

図6のタイミング差分割回路(インターポレータ)の回路構成の一例を示す図 である。

【図9】

図8のタイミング差分割回路(インターポレータ)の動作を説明するためのタ イミング図である。

【図10】

タイミング差分割回路(インターポレータ)の回路構成の別の例を示す図である。

【図11】

タイミング差分割回路(インターポレータ)の動作原理を説明するための図で ある。

【図12】

本発明の実施例で用いられる内分比可変型のインターポレータの回路構成の第 1の例を示す図である。

【図13】

本発明の実施例で用いられる内分比可変型のインターポレータの回路構成の第 2の例を示す図である。

【図14】

本発明の実施例で用いられる内分比可変型のインターポレータの回路構成の第 3の例を示す図である。

【図15】

本発明の実施例で用いられる内分比可変型のインターポレータの回路構成の第 4の例を示す図である。

【図16】

本発明の第4の実施例の構成を示す図である。

【図17】

本発明の第4の実施例の動作を説明するためのタイミング図である。

【図18】

本発明の第5の実施例の構成を示す図である。

【図19】

本発明の第5の実施例の動作を説明するためのタイミング図である。

【図20】

本発明の第6の実施例の構成を示す図である。

【図21】

本発明の第6の実施例の動作を説明するためのタイミング図である。

【図22】

本発明の第7の実施例の構成を示す図である。

【図23】

本発明の第8の実施例の構成を示す図である。

【図24】

本発明の第9の実施例の構成を示す図である。

【図25】

本発明の実施例で用いられる16等分インターポレータのレイアウトを示す図 である。

【図26】

本発明の実施例において16等分インターポレータを用いた位相調整回路の出 カのシミュレーション結果を示す波形図である。

【図27】

従来のクロック制御回路の一例を示す図である。

【符号の説明】

1 クロック

2 1/4分周回路

4 a タイミング差分割回路

4 b 多重化回路

4 c パルス幅補正回路

- 5 4相クロック逓倍回路

- 6 周期検知回路

- 7 制御信号(容量選択周波数調整信号)

- 10 逓倍用インターポレータ

- 20 ロータリースイッチ

- 30 インターポレータ(微調用インターポレータ)

- 40 制御回路

- 50 合成器

- 60 分周回路

- 101 位相調整回路

- 102、202 制御回路

- 103 分周回路

- 110 インターポレータ

- 111 デコーダ

- 112 加算回路

- 113、114 D型フリップフロップ

- 201 多相クロック発生回路

- 203 セレクタ

- 211~216 D型フリップフロップ

- 217~211 インターポレータ

- 319 位相比較回路

- 320 チャージポンプ

- 321 ループフィルタ

- 322 電圧制御発振器

- 323 分周回路

- 324 外部クロック

- 325 UP信号

- 326 DOWN信号

【書類名】 図面

【図1】

特2000-22120

【図2】

特2000-22120

【図3】

【図4】

特2000-221207

【図5】

特2000-22120

【図6】

多重化回路

特2000-22120

【図7】

特2000-22120

【図8】

(a)

**(b)**

4a2;タイミング差分割器

特2000-22120

【図9】

•

特2000-22120

【図10】

特2000-221207

【図11】

(a)

(b)

(C)

t1=CV/21 t2=T+(CV-IT)/21 t2=(1/2)T+t1 t3=T+CV/21=T+t1

特2000-221207

【図12】

【図13】

ł

【図14】

ł,

【図15】

【図16】

出証特2001-3028385

【図17】

【図18】

°,

【図19】

D

出証特2001-3028385

【図20】

U

ł

【図21】

D

1

【図22】

Ø

÷

【図24】

, D

J

【図25】

.7

Ð

Э

【図26】

9 , , , ,

¢

Ð

【図27】

【書類名】 要約書

【要約】

【課題】

ū.

۶

C

簡易な構成により、高精度に、非整数の周波数変換を行うことができるクロック制御回路及び方法の提供。

【解決手段】

入力クロック又は前記入力クロックから生成されるクロックを基準のクロック として、前記基準のクロックの周期毎に、前記基準のクロックに対する位相を、 あらかじめ所定の単位位相差分加算又は減算するための制御信号を出力する制御 回路102と、前記入力クロックを入力し、前記制御信号に基づき、前記基準の クロックに対して前記加算されてなる位相を有するクロックを出力する位相調整 回路101と、を備える。

【選択図】

図1

特2000-221207

• . \_ \_ \_

- ----

-

## 出願人履歴情報

識別番号

**њ** с! .,;

Ţ

ł

.

[000004237]

| 1. | 変更年月日  |   | 1990年 8月29日   |

|----|--------|---|---------------|

|    | [変更理由] |   | 新規登録          |

|    | 住      | 所 | 東京都港区芝五丁目7番1号 |

|    | 氏      | 名 | 日本電気株式会社      |